# Speculative execution side-channel attacks

# **Exploring cause, impact and mitigations**

# Diplomarbeit

zur Erlangung des akademischen Grades

Diplom-Ingenieur/in

eingereicht von

# Julian Simon Rauchberger is161524

| im Rahmen des                  |                                         |                            |

|--------------------------------|-----------------------------------------|----------------------------|

| Studienganges Information Sec  | curity an der Fachhochschule St. Pölter | า                          |

|                                |                                         |                            |

|                                |                                         |                            |

| Betreuung                      |                                         |                            |

| Betreuer/in: FH-Prof. DiplIng. | Dr. Sebastian Schrittwieser, Bakk.      |                            |

|                                |                                         |                            |

| Ot D"lt At C 0040              |                                         |                            |

| St. Pölten, August 6, 2018     |                                         |                            |

|                                | (Unterschrift Verfasser/in)             | (Unterschrift Betreuer/in) |

# Ehrenwörtliche Erklärung

Ich versichere, dass

- ich diese Diplomarbeit selbständig verfasst, andere als die angegebenen Quellen und Hilfsmittel nicht benutzt und mich sonst keiner unerlaubten Hilfe bedient habe.

- ich dieses Diplomarbeitsthema bisher weder im Inland noch im Ausland einem Begutachter/einer Begutachterin zur Beurteilung oder in irgendeiner Form als Prüfungsarbeit vorgelegt habe.

- diese Arbeit mit der vom Begutachter/von der Begutachterin beurteilten Arbeit übereinstimmt.

Der Studierende/Absolvent räumt der FH St. Pölten das Recht ein, die Diplomarbeit für Lehre- und Forschungstätigkeiten zu verwenden und damit zu werben (z.B. bei der Projektevernissage, in Publikationen, auf der Homepage), wobei der Absolvent als Urheber zu nennen ist. Jegliche kommerzielle Verwertung/Nutzung bedarf einer weiteren Vereinbarung zwischen dem Studierenden/Absolventen und der FH St. Pölten.

Ort, Datum Unterschrift

# Kurzfassung

Durch die Veröffentlichung der Meltdown und Spectre Schwachstellen Anfang 2018 haben Probleme, die durch unsicheres Hardware Design verursacht wurden, zusätzliche Aufmerksamkeit von Medien und Forschern erhalten. Auf Grund der Komplexität der Sicherheitslücken ist es noch immer schwerig umfangreiches Verständnis über diese Lücken zu erlangen. Diese Arbeit zielt darauf ab, sogenannte Speculative Execution Side-Channel Angriffe im Detail zu erklären. Dies geschieht durch Analyse bekannter Schwachstellen um Ursache, Auswirkungen und verfügbaren Risikominderungen festzustellen. Um auch zukünftige Auswirkungen dieser Angriffe verstehen zu können wird eine umfassende Analyse der eigentlichen Ursachen dieser Sicherheitslücken durchgeführt. Eine ausführliche Beschreibung der Hardwarekomponenten, die an Out-of-order Execution beteiligt sind, wird durchgeführt um Kernprobleme zu identifizieren und aufzulisten. Außerdem wird undokumentiertes CPU Verhalten analysiert und es werden weitere Angriffsvektoren erforscht. Eine neuartige Technik um Hardware Breakpoints, die Lesezugriff auf Speicherbereiche überwachen, zu umgehen wird vorgestellt und angewendet um ein System Management Mode Rootkit zu erkennen. Abschließend werden drei mögliche Hardwareänderungen zur permanenten Verhinderung von Speculative Execution Side-Channel Angriffen erläutert und eine Kombination aus zwei Techniken empfohlen um größtmöglichen Schutz bei geringen Performanceeinbußen zu ermöglichen.

# **Abstract**

With the public release of the Meltdown and Spectre vulnerabilities in early 2018, issues stemming from insecure hardware design have received additional attention by both media and researchers. Due to the complex nature of the vulnerabilities discussed, it is still difficult to gain a comprehensive understanding of these issues. This paper aims to shed light on so-called speculative execution side-channel attacks by analyzing cause, impact and mitigations of known vulnerabilities. To fully understand future implications of these attacks, we conduct a comprehensive analysis on their root causes. We give an in-depth explanation of hardware components involved in out-of-order execution and describe the core issues we identified. Furthermore, we reverse engineer undocumented CPU behavior and explore other attack vectors. We also demonstrate a novel technique of using speculative reads to bypass hardware breakpoints that trigger on memory reads and apply it to detect a System Management Mode rootkit. Finally, we describe three possible ways to alter hardware design to permanently eliminate speculative execution side-channel attacks and recommend a combination of them to provide in-depth protection while keeping performance impact as low as possible.

# **Contents**

| 1. | Introduction |        |                                |    |  |  |

|----|--------------|--------|--------------------------------|----|--|--|

| 2. | Background   |        |                                |    |  |  |

|    | 2.1.         | Hardw  | rare bugs                      | 3  |  |  |

|    |              | 2.1.1. | Erratum SKZ6                   | 3  |  |  |

|    |              | 2.1.2. | Erratum HSW136                 | 4  |  |  |

|    |              | 2.1.3. | The memory sinkhole            | 4  |  |  |

|    |              | 2.1.4. | Meltdown and Spectre           | 4  |  |  |

|    |              | 2.1.5. | Conclusion                     | 5  |  |  |

|    | 2.2.         | Out-of | F-order execution              | 5  |  |  |

|    |              | 2.2.1. | Out-of-order engine            | 5  |  |  |

|    |              | 2.2.2. | Speculative execution          | 6  |  |  |

|    |              | 2.2.3. | State restoring implementation | 7  |  |  |

|    | 2.3.         | Cache  | timing attacks                 | 7  |  |  |

|    |              | 2.3.1. | Practical attacks              | 8  |  |  |

|    |              | 2.3.2. | ARMageddon                     | 8  |  |  |

| 3. | Melt         | down   |                                | 10 |  |  |

|    | 3.1.         | Vulner | rability                       | 10 |  |  |

|    | 3.2.         |        |                                | 11 |  |  |

|    | 3.3.         | Meltdo | own patches                    | 12 |  |  |

| 4. | Spe          | ctre   |                                | 13 |  |  |

|    | -            |        | t 1: Bounds check bypass       | 13 |  |  |

|    | 4.2.         |        | t 2: Branch target injection   |    |  |  |

|    | 4.3.         |        | e-NG                           | 14 |  |  |

|    |              |        |                                | 14 |  |  |

|    |              | _      | Updating security boundaries   |    |  |  |

|    |              |        |                                |    |  |  |

|    | 4.5. | Patches                                                    | 15 |

|----|------|------------------------------------------------------------|----|

|    |      | 4.5.1. Retpoline                                           | 15 |

|    |      | 4.5.2. Microcode updates                                   | 16 |

| 5. | Dete | ermining root causes                                       | 17 |

|    | 5.1. | Side-channel leakage from speculative execution            | 17 |

|    | 5.2. | Microarchitectural states shared between security contexts | 17 |

|    | 5.3. | Delayed or non-existentent security enforcement            | 18 |

|    | 5.4. | Assembly instructions                                      | 18 |

|    |      | 5.4.1. PREFETCH                                            | 18 |

|    |      | 5.4.2. CLFLUSH                                             | 19 |

|    |      | 5.4.3. NON-TEMPORAL hints                                  | 19 |

|    |      | 5.4.4. RDTSC                                               | 19 |

| 6. | Ana  | lyzing the speculative execution context                   | 20 |

|    | 6.1. | Testing instruction behavior                               | 20 |

|    |      | 6.1.1. Memory read                                         | 21 |

|    |      | 6.1.2. Memory write                                        | 21 |

|    |      | 6.1.3. Memory execution                                    | 21 |

|    |      | 6.1.4. Additional findings                                 | 22 |

| 7. | Exp  | oitability of writes in speculative execution              | 23 |

|    | 7.1. | Attack scenario example                                    | 23 |

|    | 7.2. | L1 cache access                                            | 24 |

|    | 7.3. | Hyper-Threading                                            | 25 |

|    | 7.4. | Load and Store Buffers                                     | 25 |

|    | 7.5. | Analysis of hardware design                                | 26 |

|    | 7.6. | Practical tests                                            | 27 |

|    | 7.7. | Conclusion                                                 | 27 |

| 8. | Impa | act on other security boundaries                           | 28 |

|    | 8.1. | Software guard eXtension                                   | 28 |

|    | 8.2. | System Management Mode                                     | 28 |

|    | 8 3  | Conclusion                                                 | 20 |

| 9. | The    | return branch predictor                                        | 30 |

|----|--------|----------------------------------------------------------------|----|

|    | 9.1.   | Function-based control flow on x86                             | 30 |

|    | 9.2.   | Security relevance                                             | 31 |

|    | 9.3.   | Experiments                                                    | 32 |

|    |        | 9.3.1. Experiment 1: Demonstrating the existence of the RSB    | 32 |

|    |        | 9.3.2. Experiment 2: Memory location dependencies              | 33 |

|    |        | 9.3.3. Result 1: RSB length                                    | 33 |

|    |        | 9.3.4. Result 2: call-ret path mispredictions                  | 33 |

|    |        | 9.3.5. Analysis                                                | 35 |

|    |        | 9.3.6. Experiment 3: Introducing training loops                | 37 |

|    |        | 9.3.7. Conclusion                                              | 37 |

| 10 | . Alte | rnative side-channels                                          | 39 |

|    | 10.1.  | Defining side-channels                                         | 39 |

|    | 10.2.  | Choosing the violation instruction                             | 40 |

|    |        | 10.2.1. Restricted transactional memory                        | 40 |

|    | 10.3.  | Creating test code                                             | 41 |

|    | 10.4.  | Performing tests                                               | 42 |

|    |        | 10.4.1. Cache hierarchy side-channel                           | 42 |

|    |        | 10.4.2. Timing-based side-channel                              | 42 |

|    | 10.5.  | Lazy FPU bug                                                   | 43 |

|    |        | 10.5.1. Root cause                                             | 43 |

|    |        | 10.5.2. Proof of concept implementation                        | 45 |

|    |        | 10.5.3. Test results                                           | 46 |

|    |        | 10.5.4. Countermeasures                                        | 47 |

| 11 | .Вура  | assing hardware breakpoints with speculative execution         | 48 |

|    | 11.1.  | Software breakpoints                                           | 48 |

|    | 11.2.  | Hardware breakpoints                                           | 48 |

|    | 11.3.  | Implementing a proof of concept                                | 49 |

| 12 | . Lon  | g-term solutions to speculative execution side-channel attacks | 52 |

|    | 12.1.  | Approaches to a solution                                       | 52 |

|    |        | 12.1.1. Removal of offending features                          | 52 |

|    |        | 12.1.2. Preventing access to out-of-context information        | 53 |

|                                      | $\overline{}$ |

|--------------------------------------|---------------|

| 12.1.3. Removing the side-channel(s) | 53            |

| 12.2. Combined approach              | 54            |

| 13. Conclusion                       | 55            |

| A. Source Code Listings              | 56            |

| List of Figures                      | 60            |

| List of Tables                       | 61            |

| References                           | 64            |

# 1. Introduction

Speculative execution side-channel attacks are a new class of vulnerabilities which has been publicly disclosed in early 2018. Most commonly known as Meltdown and Spectre, these attacks are based on flaws found in many modern CPU architectures including x86 and ARM. As they target properties of the hardware implementation itself, they are often extremely hard if not impossible to mitigate and possibly affect billions of devices.

What makes these vulnerabilities an interesting topic of research is the fact that they expose an entirely new attack vector which has previously often been ignored in threat models as it had been deemed too unlikely to occur. With these attacks, fundamental assumptions about privilege separation at the hardware level are no longer valid. With speculative execution side-channel attacks, it is possible to cross low level boundaries such as address space isolation which have previously been considered a fundamental access control feature that serves as the base for many advanced protection mechanisms.

With knowledge about these attacks readily available to any sufficiently motivated malicious actor, it is necessary to update threat models and include mitigations to stop exploitation attempts. In order to do so, in-depth understanding of the published vulnerabilities is required. Additionally, long-term protections can only be established with a sufficient understanding of the root causes of speculative execution side-channel attacks. They do not merely represent a handful of issues that can be fixed with a set of patches but rather an ongoing field of research where new variants are discovered regularly. Furthermore, mitigations for these vulnerabilities often introduce performance penalties that strongly depend on the workload. As such, it is necessary to understand both the attack surface as well as the impact of workarounds and patches in order to deploy appropriate mitigations without unnecessarily degrading performance.

This paper aims to provide the reader with the in-depth understanding of speculative execution sidechannel attacks that is required in order to correctly evaluate threats posed by them. We give an explanation of the parts of the CPU that are responsible for out-of-order execution and eventually gave rise to the attacks described. Furthermore, we give in-depth information about the vulnerabilities, their impact and currently available patches for both Meltdown and the Spectre class of attacks. Additionally, we consider their impact on security-critical features such as Software guard eXtension and System Management Mode.

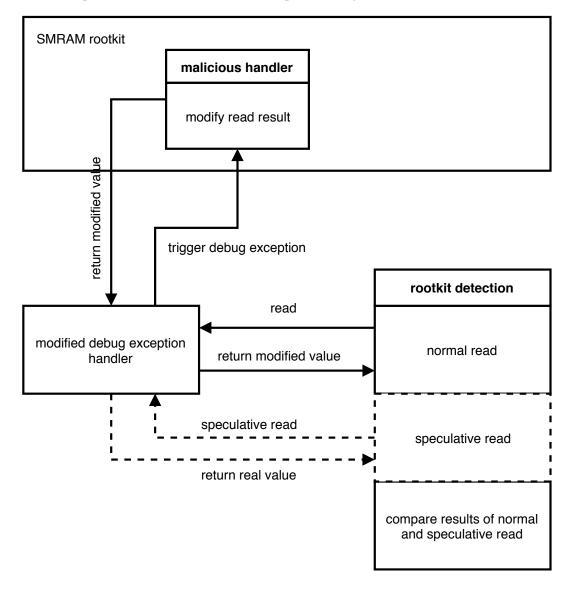

We also provide an analysis of the root causes that gave rise to these security issues and detail possible future attack surface. We analyze the behavior of speculatively running code with the aim of allowing other researchers to build upon our results. We further apply this knowledge by researching various aspects of speculative execution such as the behavior of the return branch predictor. Additionally, we investigate the possibility of creating write-based speculative execution side-channel attacks and give an in-depth explanation of the hardware components involved. We demonstrate a novel way of employing out-of-order execution to read arbitrary memory without triggering hardware breakpoints and apply the technique to detect a System Management Mode rootkit. Finally, we describe three possible ways to permanently fix speculative execution side-channel attacks by modifying the hardware design of the CPU.

The main contributions of our paper are:

- a detailed root cause analysis of speculative execution side-channel attacks, including software impact and hardware design

- in-depth description of various actual vulnerabilities such as Meltdown, Spectre and the lazy FPU bug

- analysis of possible future attack surface such as write-based attacks and poisoning of the return predictor

- a novel root kit detection technique using speculative reading of memory

- possible design modifications to mitigate the described attacks

# 2. Background

For a holistic assessment of speculative execution side-channel attacks, it is necessary to understand the complex hardware details that gave rise to these vulnerabilities. Additionally, observing historic hardware issues with security impacts allows for a better understanding of the threat generally posed by such issues.

## 2.1. Hardware bugs

Although not exactly common, bugs stemming from erroneous hardware design have affected computer systems for a long time. For instance, in 1994, the infamous Pentium FDIV bug caused affected processors to produce incorrect floating-point numbers when executing certain divisions. This ultimately led to Intel recalling the flawed units, costing them millions<sup>1</sup>. While this bug did not cause any immediate security issues, there have been others which could have led to such concerns.

#### 2.1.1. Erratum SKZ6

In 2016, developers of the OCaml programming language encountered an obscure hyper-threading bug affecting Skylake and Kaby Lake processors which they later documented in public blog posts after Intel had released a microcode update to address the issue [1, 2]. The errata released by intel describes the problem as following:

"Under complex micro-architectural conditions, short loops of less than 64 instructions that use AH, BH, CH or DH registers as well as their corresponding wider register (e.g. RAX, EAX or AX for AH) may cause unpredictable system behavior. This can only happen when both logical processors on the same physical processor are active." [3]

While the exact impact of the bug is not immediately clear, it seems very likely that under the conditions described, one logical hyper-threading core can corrupt or otherwise influence the registers of the other sibling core. To the best of the authors knowledge, no public demonstrations of the exploitability of this bug exist. It is very likely that that the bug is practically unexploitable because of how hard it is to

<sup>&</sup>lt;sup>1</sup>http://www.trnicely.net/pentbug/pentbug.html

trigger in a meaningful way, however it clearly demonstrates how hardware bugs can break fundamental privilege boundaries. The OCaml developer that first analysed the issue also notes that on at least one occasion, page tables of the operating system were corrupted by the bug. This clearly proves that privilege escalation is, at least theoretically, possible.

#### 2.1.2. Erratum HSW136

From a security point of view, another notable hardware bug is Erratum HSW136 [4], which led Intel to disable the newly introduced Transactional Synchronization eXtension (TSX) feature on certain affected CPUs. While details on the issue are sparse, it can be assumed that the impact must have been relatively severe if it led to Intel disabling an entire CPU feature. TSX can be used to implement transactional memory operations at the hardware layer and can be a significant performance improvement for multi-threaded code that relies heavily on locking. With TSX, multiple memory addresses can be modified within a transaction without the changes being visible to other threads. Then, all modifications can be committed with a single instruction or alternatively rolled back. Incorrect implementation of such a feature could lead to unexpected race conditions or maybe even corruption of arbitrary memory if permission checks aren't working correctly.

#### 2.1.3. The memory sinkhole

In 2015, Christopher Domas demonstrated an attack where the memory holding the Local Advanced Programmable Interrupt Controller (LAPIC) registers is remapped into a memory region otherwise inaccessible to even the operating system kernel known as System Management RAM (SMRAM) [5]. By carefully shadowing a key data structure, a Global Descriptor Table (GDT) under the attackers control will be loaded and ultimately result in execution resuming outside of SMRAM. This attack shows that even a relatively weak primitive that allows only to set a small region of memory to zero allows a skillful attacker to escalate privileges.

#### 2.1.4. Meltdown and Spectre

Probably the most widely known example of hardware security issues with far-reaching consequences are the Meltdown and Spectre bugs discovered independently by Google Project Zero, Cyberus Technology and Graz University of Technology. Publicly disclosed in January 2018, these vulnerabilities brought the importance of securely designed and correctly implemented hardware to the eye of the public. Both were practical, exploitable bugs with very real consequences but no easy solution. Careful balancing between effectiveness and performance impact had to be done when implementing patches. It was also

discovered that the same or similar problems could be found in many other architectures such as ARM or x86 CPUs manufactured by AMD. In the following months, other researchers discovered and published papers on variants of the initial vulnerabilities [6] [7].

The chapters 3 and 4 provides an in-depth analysis of the inner workings of these vulnerabilities and the principles they are based on.

#### 2.1.5. Conclusion

While this is by no means a comprehensive list of issues caused by hardware bugs, the examples clearly demonstrate the massive threat that they can pose. All these security issues highlight how hard it is to respond to threats that break the very foundations operating systems base their security on. Kernel as well as userland software completely relies on the correct implementation of certain security features at the hardware layer. If these assumptions do not hold, system confidentiality, integrity and availability can no longer be guaranteed. Unlike software-based security issues, these bugs affect an even larger number of systems and can be very hard or even impossible to patch. As described in the examples above, responses ranged from simple microcode updates over selective disabling of features up to the costly recalling of entire product lines. More research and responsible disclosure is needed to ensure potential security issues are identified and fixed in a timely manner.

#### 2.2. Out-of-order execution

To increase the utilization of all of its components, modern processors make use of out-of-order execution. This means that instructions are not necessarily executed in the same order as they appear in the instruction stream. Since different components of the CPU are used for different computations such as additions, multiplications or memory access, instructions can sometimes be executed in parallel. Many processors also possess extensive circuitry to detect dependencies between operations and can therefore reorder operations to increase utilization and throughput while still producing the correct output. A reorder buffer is used to ensure that even though actual execution is out-of-order, the instructions retire in the same order they were originally issued [8].

#### 2.2.1. Out-of-order engine

The actual hardware responsible for out-of-order execution is called the Out-of-order engine as described in the Intel 64 and IA-32 Architectures Optimization Reference Manual [9]. It splits the instruction stream into dependency chains which are then sent to execution. If one dependency chain has to wait for

a resource such as an L2 cache entry, another dependency chain can be executed in the meantime. The Out-of-order engine consists of three major parts working together: the *renamer*, the *scheduler* and the *retirement component*.

The *renamer* connects the incoming in-order view of the instruction stream to the scheduler. It is responsible for moving micro-ops from the micro-op queue to the Out-of-order engine. During this process, it also renames architectural sources and destinations to micro-architectural sources and destinations, hence the name of this unit. At very low levels, the CPU does not work with traditional register names programmers are used to but rather dynamically reassigns them to a larger set of internal micro-architectural registers. Additionally, resources like load and store buffers are allocated to the micro-ops at this point. The renamer is also able to detect and remove false dependencies. An example of this would be the XOR RAX, RAX instruction. Even though it operates on the RAX register, the result will always be zero and therefore not depend on the initial value of RAX. The renamer can detect and correctly remove such Dependency Breaking Idioms to ensure they do not affect out-of-order execution negatively.

The *scheduler* is responsible for dispatching micro-ops to the execution core. It identifies which micro-ops are ready and have all required input available and then selects which of those are dispatched every cycle.

When an instruction has completely been executed and it is certain that no faults or exceptions that would invalidate the result occurred, they are retired. This means that their results take actual effect and will be visible to the outside world. This process is the responsibility of the *retirement component* which also ensures that micro-ops retire in the same order they were issued.

#### 2.2.2. Speculative execution

When out-of-order execution reaches a point where the CPU cannot be sure which way to continue, speculative execution is employed. This happens for instance because of a branch that depends on a memory location that is not in the cache. Since it is not yet known where in memory the next instruction will be and waiting for the memory load would be too time consuming, the branch prediction unit is used to take a guess. Execution is then continued there. In the best case, the prediction is later shown to be correct and the executed instructions can be retired normally. If not, everything after the branch has to be abandoned and the correct path has to be executed. This is usually done by creating a checkpoint at the time of the branch and later reverting the CPU state to this checkpoint. For the sake of simplicity, we will refer to this process as "snapshots" and "rollbacks" within this paper.

#### 2.2.3. State restoring implementation

At the hardware level, restoring an older CPU state requires two separate mechanisms. The first is to ensure that register modifications can be rolled back, and the old state of all registers can be restored. This is implemented through *register renaming*. Internally, the processor has many more physical registers than those which are logically exposed to the programmer. These so-called micro-architectural registers can be dynamically assigned to the logical registers. To implement the concept of a register snapshot, the CPU stores at a given point in time the association between logical and micro-architectural registers and ensures that these do not get modified. The CPU then proceeds to work only with the other micro-architectural registers which are not part of the snapshot during speculative execution. If the speculated instructions retire, the snapshot metadata can be discarded. In case of a rollback, all modifications are discarded instead, and the registers are restored from the saved state. The second mechanism required to implement snapshots deals with memory writes as these also have to be able to be undone. This is implemented through the use of buffers which store the modifications before they are committed to main memory. In case of a rollback, the contents of the buffers can simply be discarded.

Branch mispredictions generally have a rather large performance penalty as not only the results of already executed calculations have to be thrown away but also the correct ones have to be executed from scratch. Because of this, there is a large incentive to ensure branches are correctly predicted, resulting in complex algorithms being used by the branch prediction units.

To avoid repetitions of the same topic, when we refer to speculative execution within this paper, we generally mean instructions that are being executed but have not been retired yet and might still be abandoned, including normal out-of-order execution that does not directly depend on branch prediction.

# 2.3. Cache timing attacks

At the core of both Meltdown and Spectre are timing-based side-channels that can leak information from the speculative execution context. While these attacks are by far the most prominent and have an arguably very high impact, the idea of using microarchitectural timing differences to breach security boundaries is not new. Historically speaking, these side-channels have mostly been used to defeat *Kernel Address Space Layout Randomization* (KASLR). With KASLR, the operating system kernel gets loaded at a new, randomized address during each boot. By using a variety of different techniques to access random memory addresses in kernel space and measuring the access times, researchers found various ways to differentiate between mapped and unmapped areas. In some cases, it is even possible to get additional information about a given memory area.

#### 2.3.1. Practical attacks

In 2013, Hund et al. demonstrated multiple timing-based side-channel attacks that disclose information about the kernel memory [10]. The usage of memory access time differences based on the cache level the data can be found in is very similar to the techniques used in the Meltdown and Spectre attacks. Similar techniques have also been previously described by researchers from Graz University of Technology [11]. The *DrK* attack, developed by Yeongjin Jang et al., makes use of the Intel TSX feature to suppress exceptions normally raised by access violations when code with userland privileges tries to access kernel memory [12]. They found that measuring timing of the execution of the TSX abort handler is much more accurate than doing the same with an exception handler. The attack can not only differentiate between mapped and unmapped areas but also between executable and non-executable.

The x86 architecture is especially susceptible to these attacks because it provides all the necessary tools to unprivileged code by default. Instructions of the CLFLUSH family can be used to reliably remove a given memory address from cache. Additionally, multiple PREFETCH instructions exist that can be used to load a memory address into any given cache level at will. With RDTSC, attackers have access to a high-resolution timer that greatly simplifies many attacks. Even though unprivileged access to this instruction can be disabled, there is no major operating system that does so to the best of the authors knowledge. Multiple strategies for cache attacks have been identified in the past, including *Evict+Time* [13], *Prime+Probe* [13] and *Flush+Reload* [14].

#### 2.3.2. ARMageddon

Even though specialized assembly instructions make certain attacks easier, it is also possible to exploit timing-based side channels without them, as demonstrated by the *ARMageddon* attacks [15]. They are based on selectively flushing certain shared memory code from cache to determine which code has been executed by other applications. This is used to spy on smartphone users by flushing code that handles different user interactions such as gestures and key presses. Depending on which parts of the code get cached again, attackers can get some understanding of how the victim interacts with the smartphone. Contrary to most of the previous attacks which were focused on Intel CPUs, ARMageddon works on the ARM architecture. The authors did a comprehensive study on the cache eviction policy used by widespread ARM CPUs and were able to reverse engineer the algorithm. This allowed them to remove a given address from cache by accessing and thereby caching other addresses in a way that causes collisions in the cache. With knowledge of the caching algorithm it is possible to execute caching-based attacks even though there is no dedicated flush instruction on most ARM CPUs. Unlike x86, the ARM architecture also does not contain a high-resolution timer with unprivileged access that could be used

to determine access times. The authors provide multiple alternative ways such as performance events or a dedicated thread timer to solve this problem. ARMageddon clearly demonstrates that cache-based side-channels can also be exploited on Architectures that do not provide a dedicated flush instruction and a high-resolution timer.

# 3. Meltdown

The *Meltdown* [16] vulnerability affects most modern Intel CPUs and also some ARM processors. According to AMD, Meltdown does not apply to their products due to differences in processor design<sup>1</sup>. It allows unprivileged users to disclose kernel memory from Ring 3 by using a side-channel during speculative execution and thereby breaks all security assumptions given by address space isolation. On some architectures, Meltdown can also be used to read privileged registers, but this paper focuses on the Intel x86 architecture where this is not true.

## 3.1. Vulnerability

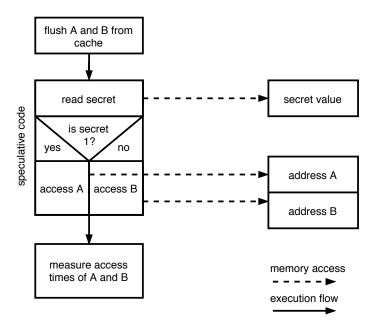

Meltdown is a form of race condition between fetching an address and completing the permission check. When accessing a memory address the code lacks permission to read, out-of-order execution allows multiple instructions to be executed before the violation is detected. At that time, all modifications based on the value read will be invalidated and the state of the CPU will be rolled back. If implemented correctly, this would be enough for Meltdown to be unexploitable as the result of the fetch would not be available to the attacker. The vulnerability lies in the fact that changes in some microarchitectural states will not be correctly rolled back and can therefore be used as a side-channel to leak information. In the original paper, this side-channel has been the cache hierarchy. By selectively accessing memory and therefore fetching it into cache during out-of-order execution, the researchers were able to leak data one bit at a time. To give a simple example, an attacker could access address A if the secret value is 1 or address B if it is 0. By measuring access times to these locations after the rollback, an attacker would be able to establish a side-channel. This attack scenario is detailed in Figure 3.1. It is currently not clear if and how many other microarchitectural side-channels exist.

<sup>&</sup>lt;sup>1</sup>https://www.amd.com/en/corporate/security-updates

Figure 3.1.: Meltdown attack

### 3.2. Impact

Meltdown breaks privilege-based separation of kernel and userland memory, more specifically the protection provided by the page tables. The page tables are a hierarchical memory structure set up by the kernel that defines the mapping between physical and virtual addresses. The configuration defined in the page tables is then enforced by the Memory Management Unit (MMU). Each entry contains a *User/Su*pervisor (U) bit which is a flag that controls if the page can be accessed from the userland or requires Ring 0 privileges. This normally prevents unprivileged code from reading data from kernel memory but the Meltdown vulnerability breaks this assumption. Research conducted by Google Project Zero [17] indicates that not all kernel memory can be read with Meltdown but rather requires a precondition. They assume this to be presence of the targeted kernel memory in the L1 data cache but do not hold complete confidence in this statement. It seems however reasonable that Meltdown requires the targeted data to be in the cache hierarchy as fetches from main memory typically require around 200 CPU cycles and are therefore too slow to be completed during the short time window between creation of the violation and enforcement that Meltdown is based on. Additional research indicates that Meltdown cannot be used to cross other privilege boundaries such as Intel Software Guard eXtension (SGX) [6] and System Management Mode (SMM)<sup>2</sup>. This indicates that the Meltdown vulnerability only affects the protections normally provided by page table isolation and is not a more general bypass that can be used to read any protected memory locations.

<sup>&</sup>lt;sup>2</sup>https://blog.eclypsium.com/2018/05/17/system-management-mode-speculative-execution-attacks/

## 3.3. Meltdown patches

The Linux kernel fixes the Meltdown vulnerability with the *kernel page-table isolation* (KPTI) workaround which is based on the older set of *KAISER* (Kernel Address Isolation to have Side-channels Efficiently Removed) patches originally presented in a paper by Gruss, Lipp, Schwarz, Fellner, Maurice and Mangard [18].

The idea behind KPTI is to work around the incomplete protections provided by page tables in light of Meltdown by unmapping as much as possible of the kernel code and data regions while userland code is running. Instead of only using one set of page tables, KPTI introduces a second set. When kernel code is running, the original set that includes both kernel and userland regions is used. When execution passes to unprivileged Ring 3 code, a second set that maps only userland memory and a minimal amount of kernel code to handle syscalls, interrupts and exceptions is being used. Since Meltdown can only be used to read cached and mapped kernel memory, this completely protects against the vulnerability at the cost of performance. The exact impact is hard to measure as it depends heavily on the workload and also on the CPU generation. One of the biggest reasons KPTI impacts performance is the requirement of a translation lookaside buffer (TLB) flush during each context switch. As the kernel memory gets temporarily unmapped, the cached mapping entries have to be removed from the TLB as well. This also means they will not be available the next time kernel code runs, strongly limiting the positive effect TLB normally has on address translation performance. This can be avoided by making use of the processorcontext identifiers (PCID) hardware feature which Linux fully supports since Kernel version 4.14. PCID allows to tag TLB entries with a context identifier that can be used to dynamically control access to the entries. It limits TLB lookups to the currently allowed context. By using different PCIDs during kernel and userland execution, the kernel TLB entries can be made invisible to lower privilege levels without having to flush them. On older processors not supporting PCID, the performance impact of KPTI is therefore much bigger. To the best of the authors knowledge, the page table isolation software workaround is at the time of writing the only possible protection against Meltdown on affected Intel processors. No microcode updates that address Meltdown specifically have been released but Intel has stated that an upcoming hardware redesign will feature protections against Meltdown.

Both the Windows and MacOS operating systems have implemented Meltdown fixes in a similar fashion to Linux. Microsoft states that performance impact is negligible on Windows 10 PCs with Skylake, Kabylake or newer processors. Haswell or older shows a more significant slowdown, especially when paired with an older version of Windows<sup>3</sup>.

<sup>3</sup>https://cloudblogs.microsoft.com/microsoftsecure/2018/01/09/understanding-the-performance-impact-of-spectre-and-meltdown-mitigations-on-windows-systems/

# 4. Spectre

While Meltdown can be very clearly defined and worked around, *Spectre [8]* describes a full class of vulnerabilities with many variants, some of which have been discovered after the original paper had been published. Spectre attacks are based on maliciously inducing branch mispredictions in a way that benefits the attacker by crossing security boundaries. Depending on the variant, this can be done either directly or by mistraining a branch predictor.

## 4.1. Variant 1: Bounds check bypass

Variant 1 is also known as *bounds check bypass* (BCB) and summarizes attacks where a check is bypassed during speculative execution because the CPU wrongly assumes the check will succeed. This can for instance happen if the user is able to specify an index for an array and the code first checks if the index is within the bounds of the array. By doing multiple runs with an in-bounds index, the branch predictor can be trained to assume that the check will succeed, and the array access will subsequently be executed. Afterwards, an out-of-bounds index is supplied, the branch prediction will assume that the bounds check will succeed again and speculatively run the array access code with an invalid index, ultimately accessing data outside the array. The attacker must then find a way to leak the accessed data through a cache side-channel. This attack is most relevant in the scenario of untrusted code running inside a sandbox, e.g. *JavaScript* in a web browser. Under these circumstances, Spectre variant 1 has been demonstrated to be able to read arbitrary browser memory which might contain secrets such as cookies or passwords.

## 4.2. Variant 2: Branch target injection

Variant 2, branch target injection (BTI), is described as an attack scenario where the internal state of the branch predictor is manipulated to ensure that branch prediction will predict an address favorable to the attacker. If successful, this attack can essentially be used to speculatively execute arbitrary code in the context of the poisoned branch instruction. This vulnerability can most easily be exploited with indirect branches and has been demonstrated to be able to leak data from one process to attack code running in

another.

## 4.3. Spectre-NG

Eight new Spectre variants, dubbed Spectre-NG<sup>1</sup>, have been announced in May 2018, however at the time of writing only two of them have been publicly released. Variant 3a, known as *rogue system register* read affects systems that allow speculative reads of system registers and can allow attackers to read their contents by employing the same side-channels used in other Spectre attacks. Variant 4, *speculative store* bypass, is based on processors speculatively reading memory before the addresses of all prior writes are known which may lead to the reading of an earlier value.

## 4.4. Impact

Spectre highlights a critical issue: the sharing of architectural states between code running in different security contexts, for instance branch prediction tables shared between processes running as two different users. A malicious user could deliberately craft jumps to poison the branch prediction table in a way that incorrectly predicted branches in the process of another user. Similar to the side-channels employed in Meltdown, these mispredictions could then cause the leakage of information. A commonly demonstrated way to exploit this is by bypassing array bounds checks. If no mitigations are present and exploitable gadgets exist, Spectre can theoretically be used to read all memory present on the system. Like Meltdown, this requires an attacker to be able to execute arbitrary code on the system.

Spectre is known to affect most advanced CPUs that have some sort of dynamic branch prediction. This includes Intel and AMD, some high-performance ARM CPUs and possibly others. At the time of writing, the full range of affected devices is still being discovered.

#### 4.4.1. Updating security boundaries

Spectre/Meltdown has led to an update of the threat model used by the Chromium developers. They now consider all active web content such as *JavaScript*, *Flash* or *WebAssembly* as being able to abuse side-channels to read all data hosted in the same address space<sup>2</sup>.

In the light of Spectre, it is necessary to reconsider many traditionally uncrossable security boundaries. Theoretically, Spectre can be used to read any memory on the system if vulnerable code runs at any

<sup>&</sup>lt;sup>1</sup>https://www.heise.de/ct/artikel/Exclusive-Spectre-NG-Multiple-new-Intel-CPU-flaws-revealed-several-serious-4040648.html

<sup>&</sup>lt;sup>2</sup>https://chromium.googlesource.com/chromium/src/+/master/docs/security/side-channel-threat-model.md

time and has access to the targeted data. As the side-channels exploited by Spectre have historically not been considered when implementing code, it should be assumed that all code written previously to the discovery of Spectre is vulnerable. Without hardware-based fixed provided by CPU vendors, it is only possible to limit the impact of Spectre as much as possible by making exploitation harder to the point where it becomes infeasible. As long as the underlying architecture-state sharing has not been fixed, an attacker with enough resources should be assumed to be able to write a functioning exploit for Spectre. In contrast to Meltdown, which can only be used to bypass page table-based isolation between userland and kernel, Spectre has a much wider range of impact on privilege boundaries. It can be used to read memory from protected region in the same process (e.g. memory normally not accessible by a JavaScript engine), other processes, the kernel and other protection mechanisms such as SGX. However, many of these attacks are extremely hard to execute and while proof of concept implementations exist, there is no known account of in-the-wild exploitation where actual meaningful data has been compromised. To give an example, Spectre theoretically allows JavaScript hosted on a website to manipulate the branch predictor in a way that attackers can read a text document opened in another program. Practically speaking, this attack is currently infeasible as there are too many unknown variables such as CPU generation, microcode version, address space layout randomization and the scheduler that would need to be accounted for. Implementing a reliable attack that works on multiple systems seems almost impossible, but it could theoretically be done with enough resources which is why Spectre should still be considered as a vulnerability that needs to be addressed.

#### 4.5. Patches

Finding workarounds for Spectre vulnerabilities is not as straightforward as with Meltdown. As it is extremely hard if not impossible to determine the full scope of all Spectre vulnerabilities and new variants are still being discovered, it cannot be said that Spectre has been fully mitigated at the time of writing. While certain protections exist, and exploitation has become harder, it is very likely that this will stay a topic of research for the foreseeable future.

#### 4.5.1. Retpoline

Compilers have been updated to include the *Retpoline* feature which protects indirect jumps by replacing them with return statements and adding an endless loop that will never be executed during runtime but which the CPU will predict as the correct branch target, thereby trapping speculative execution. While

being a valid mitigation in some cases, Retpoline cannot provide protections under all circumstances<sup>3</sup>. It should be noted that on Skylake and newer processors, the return branch predictor has a fallback mechanism that will use the branch target buffer to predict branches when the return stack buffer underflows. This means that on these systems, retpoline cannot be seen as a reliable protection mechanism and needs to be supplemented by hardware-based protection<sup>4</sup>.

#### 4.5.2. Microcode updates

Intel has issued Microcode updates for modern CPUs which further mitigate known issues. Several additional CPU features were introduced that can help kernel developers protect against Spectre-style attacks.

The newly introduced *indirect branch restricted speculation* (IBRS) is meant to provide protection against certain attacks based on variant 2, the branch target injection. When IBRS is active, predicted target addresses cannot be influenced by code that executed in a less privileged prediction mode before that IBRS mode was last set to one<sup>5</sup>. This means IBRS can be used to protect branch prediction in the kernel from code running in userland.

The second new feature, *single thread indirect branch predictors* (STIBP) stops sibling hyperthreading cores from influencing indirect branch prediction on each other. This is especially important since hyperthreads share more hardware resources than physicall cores on a processor do. Providing logical separation between them is something that can only be done at the processor level and not by the operating system [19].

Another new feature, the *indirect branch prediction barrier* (IBPB) can be used to flush the branch prediction state at any time and completely reset it. Operating systems can use this feature to ensure code running previously has no impact on code running afterwards. The kernel can for instance use this to reset the branch prediction table and associated data structures when it switches execution from one process to another. This however comes with a non-negligible performance impact and should therefore only be used where absolutely necessary<sup>6</sup>.

All of the new features described here have been delivered to supported CPUs through microcode updates. This of course means that it is crucial for security to deploy these updates in a timely fashion because even if operating systems support the techniques, they cannot make use of them if the underlying microcode does not yet include them.

<sup>&</sup>lt;sup>3</sup>https://lkml.org/lkml/2018/1/4/724

<sup>&</sup>lt;sup>4</sup>https://lkml.org/lkml/2018/1/4/724

<sup>&</sup>lt;sup>5</sup>https://lwn.net/Articles/743019/

<sup>&</sup>lt;sup>6</sup>https://patchwork.kernel.org/patch/10145335/

# 5. Determining root causes

In order to determine where further attack vectors in the Intel architecture might be located, it is first necessary to determine the key issues that lead to the exploitability of Meltdown and Spectre. We identified three core findings than can be used as a starting point for further research:

- 1. Side-channel leakage from speculative execution

- 2. Microarchitectural states shared between security contexts

- 3. Delayed or non-existentent security enforcement

The following sections explain these findings in more detail.

# 5.1. Side-channel leakage from speculative execution

None of the vulnerabilities exploited in Meltdown and Spectre attacks would have any real-world impact if it were not possible to leak information obtained during speculative execution to code running outside of this context. The core issue here is that the complete architectural state at the beginning of speculative execution is not restored during a roll back to a previous checkpoint. This is specifically exploited by abusing the fact that cache loads occurring during speculative execution are not evicted upon a roll-back. This can be used to leak the obtained information. For instance, by either accessing address A if a 1 is encountered or address B if 0 is encountered. It can then later be determined which address had been accessed by measuring load times to determine if it can be found in the CPU cache. It is very likely that cache loads are not the only microarchitectural state that is not reset during a roll back. Further research is required to determine if information can also be leaked in other ways.

## 5.2. Microarchitectural states shared between security contexts

The second issue is that internal information recorded on certain events such as branches can influence code running in other security contexts. For instance, it is possible that branches taken in process A influence the prediction behavior in process B. This allows a malicious user to manipulate prediction

behavior in other contexts. By combining this with a leaking side-channel, it is possible to obtain information otherwise protected from access. The problem here is that internal CPU states are shared between different contexts, can be modified by any of them and in turn influence behavior in other contexts. It remains to be determined how many of these internal states exist and which can be manipulated in ways that have impact on the security of the system. It would be especially interesting to see if there are shared states that are not related to the branch prediction tables exploited in Spectre attacks.

## 5.3. Delayed or non-existentent security enforcement

The Meltdown attack is based on the fact that it is possible to access otherwise restricted memory regions during speculative execution and also execute additional instructions before the access violation is enforced. In combination with a leaking side-channel, this allows to acquire information otherwise unobtainable and persist some of it in way that is not reset by a roll back. The core problem here seems to be that it is possible to execute additional instructions between the occurrence of the access violation and retirement of the instruction block. In other words, enforcement of access control is delayed instead of immediate during speculative execution. Further vulnerabilities beside reading of unauthorized memory areas might exist. Meltdown demonstrates that code executed during speculative execution does not behave as it would be expected if the system were only doing simple in-order execution. Further analysis is required to determine if there are any additional enforcement differences that could be used by bypass security boundaries.

# 5.4. Assembly instructions

Additionally, it should be noted that a range of assembly instructions exists on the x86 platform that can simplify exploitation of Spectre and Meltdown type vulnerabilities. Even if they are not strictly required in most cases, we consider them part of the attack surface as they make both discovery and exploitation significantly easier and might make attacks on otherwise unexploitable vulnerabilities more realistic. The following section gives an overview of these instructions and explains which benefits they provide for attack scenarios.

#### 5.4.1. PREFETCH

This family of instructions allows an unprivileged user to fetch memory into the CPU cache. Multiple variants exist that affect different layers of the cache hierarchy. While of course not strictly necessary to

execute attacks on speculative execution, this gives an attacker detailed control about the cache and can thus be beneficial.

#### 5.4.2. CLFLUSH

CLFLUSH removes memory at the given address from all levels of the cache hierarchy. Researchers have demonstrated that the same effect can also be achieved by selectively accessing certain memory locations in order to get an address of their choosing evicted from cache [15]. This however requires extensive understanding of the eviction strategy used by the CPU which is time consuming to reverse engineer and might differ between models or generations. CLFLUSH provides a simple and portable means, greatly simplifying attacks that require certain memory locations to be uncached.

#### 5.4.3. NON-TEMPORAL hints

The Intel architecture contains several variants of MOV instructions which contain a "non-temporal hint", for instance MOVNTI. When these instructions are used to read or write memory, the CPU will not fetch the corresponding line into the cache hierarchy. This can be helpful for attackers when they want to ensure that auxiliary code does not pollute the cache.

#### 5.4.4. RDTSC

This instruction can by default be executed from userland code (Ring 3) and allows access to a high-resolution timer. The EDX and EAX registers are filled with a timestamp counter with a combined resolution of 64 bit. This counter is incremented by the processor at every clock cycle and thereby provides an extremely accurate measurement of timing differences, making it very valuable for determining memory access delays. While RDTSC makes attacks easier to implement, it should be noted that there are also other ways of getting high resolution timers for the same purpose, for instance a thread that increments a single integer as fast as possible. While this method does not have the same reliability, it seems to work well enough for actual attacks in practice [20].

# 6. Analyzing the speculative execution context

The Meltdown vulnerability shows that the *out-of-order context* that speculatively executed code runs in, differs significantly from the regular, well-documented *in-order view* programmers are normally working with. After out-of-order execution has completed, the reorder buffer ensures that the instructions retire in the correct order so that the actual result is not influenced. It is however also possible for faults and violations to occur during out-of-order execution, and in these cases, some behavior has been shown to differ. The reorder buffer ensures that these divergences from expected behavior do not influence the in-order result of a computation by throwing away the results of instructions executed after an exception occurred in regard to the in-order sequence. However, these instructions have still been executed at some point, even if their results are not made visible.

The authors of Meltdown discovered that one of the differences between out-of-order execution and inorder execution is that it is possible to read kernel memory and continue executing instructions for a few cycles before the violation is detected. It seems likely that there are additional differences in the behavior of code during speculative or out-of-order execution. For the purpose of this research, we will refer to this as the *speculative context* and attempt to discern differences in behavior of assembly instructions when running in this context.

# 6.1. Testing instruction behavior

In order to test the behavior of instructions in the speculative context, we must first write code that creates a branch misprediction in order to execute code speculatively. We can then leak the results of our tests through selective cache loads and discern differences from expected behavior. As branch predictor behavior differs between processor generation, we focus on the Haswell test system used for this research. To intentionally induce a branch misprediction, we create a program that contains a loop which will run n times. During each iteration, an if condition in the loop either executes code or jumps over it. The condition is set up to ensure that the code will execute during the first n-1 iterations and

be skipped during the last. Additionally, the condition depends on memory that will be flushed from cache during each iteration. This setup ensures that the code inside the if will be speculatively executed during the last iteration and subsequently be rolled back because the CPU will eventually detect the misprediction. We can then leak data from this speculative execution context by selectively accessing one of two addresses during the last iteration. The first signifies a binary one, the second a binary zero. After speculative execution is complete, we can use the RDTSC instruction to approximate how many cycles access of each memory location takes. If an address had been accesses during speculative execution, it should already be in the cache hierarchy, making later accesses significantly faster.

The results of the tests run using this setup on a Haswell CPU are described in the following sections.

#### 6.1.1. Memory read

It was possible to directly and accurately read kernel memory from userland as described in the Meltdown paper. We found that only memory which already resides in the cache hierarchy can be read. This is most likely because access to uncached memory locations takes so many cycles that the CPU will detect the branch misprediction and abort speculative execution before the load can complete. Additionally, it seems to also be possible to read from completely unmapped memory locations. During our tests, these reads always resulted in the value zero, but code continued to execute speculatively after the access. We assume that page faults have a delayed effect, similar to segmentation faults. Of course, it is also possible to read every address of the normal process memory.

#### 6.1.2. Memory write

#### 6.1.3. Memory execution

It is possible to jump to other memory locations and continue execution there as long as the instructions are valid and the memory is mapped with the executable permission. It is not possible to speculatively execute memory that lacks the executable flag, even if it is in userland. Furthermore, we conducted additional tests regarding access of userland data from speculatively executed kernel code. *Supervisor mode*

execution prevention (SMEP) is a hardware feature found in in modern Intel processors that prevents the execution of userland code from Ring 0 and has been introduced to make privilege escalation exploits harder. We conducted tests to determine if SMEP also stops speculative execution. We implemented the same test software described above as a Linux kernel module and tested it on an install of Ubuntu 16.04. We found that it is not possible to speculatively execute userland code from ring 0 if SMEP is active. It seems that this protection mechanism takes precedence over speculative execution. Unfortunately, our tested processor did not support *supervisor mode access prevention* (SMAP) and speculative userland read/write protection from Ring 0 could not be tested.

#### 6.1.4. Additional findings

We found that many instructions – mostly those that require a higher privilege level to execute – immediately stop speculative execution. Contrary to read or write permission violations which didn't stop execution under any circumstance in our tests, any instruction placed afterwards will not run. This includes for instance any and all accesses to control registers (e.g. MOV RAX, CR0), machine specific registers (RDMSR, WRMSR), the global descriptor table (LGDT, SGDT) and SYSCALL.

# 7. Exploitability of writes in speculative execution

Considering the flaws Meltdown and Spectre are based on, we considered the possibility to exploit not only memory *reads* but also *writes* during speculative execution. One of the core issues in Meltdown is that the permission check does not have immediate effect when reading kernel memory from cache during speculative execution. Before the access violation aborts and rolls back speculative execution, additional instructions that leak the contents of the read can be executed. This allows an attacker to leak arbitrary data from CPU cache.

Based on this, it seems reasonable that attacks based on cache writes could also exist. It should be possible to write arbitrary data to memory locations and execute additional instructions before the access violation aborts speculative execution. To exploit this in a real-world scenario, one would need to find a way to influence code outside of speculative execution with these modifications. It might be possible to manipulate cache lines inside speculative execution on one core in a way that, also speculatively executed code, running on another core at the same time will be influenced. Most likely this would be detected by the CPU, and the corresponding changes rolled back, but the same techniques used in Meltdown leaks could be applied to read arbitrary memory in other contexts.

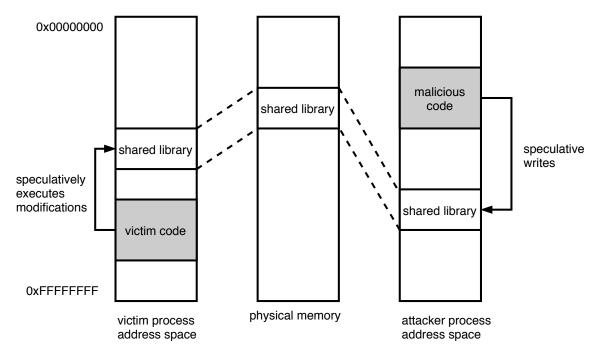

# 7.1. Attack scenario example

To give an unlikely but easy to understand example, it could be possible to modify shared code backed by the same physical memory during speculative execution running on core A. If core B runs speculative execution within a victim process that uses the same shared code, at the same time, those changes might be visible. As soon as the access violation from core A is processed by the CPU, all changes would be rolled back so if this happened accidentally, no corruption would occur. If an attacker were to specifically craft the code, they could read arbitrary memory in the victim process and leak it through cache-loads like in Meltdown. The described scenario is depicted in Figure 7.1This exact scenario is not very likely to work, but it should be a simple example of the type of attack being proposed here: since it is possible

to modify arbitrary memory during speculative execution and continue executing additional instructions before the modifications are rolled back, it might be possible to influence code running on other cores at the same time. This is especially true for hyper-threading enabled CPUs as logical cores share many resources that physical cores do not.

Figure 7.1.: Speculative write attack scenario

In order to evaluate the probability of this scenario, it is necessary to gain a deeper understanding of CPU caches on the Intel platform. The following sections give the necessary background information to evaluate the probability of the proposed attack.

#### 7.2. L1 cache access

On recent Intel CPUs, the *L1 cache* is virtually-indexed and physically-tagged<sup>1</sup>, this means that the offset bits of the virtual address are used to calculate L1 array locations. Since the offset bits are the same in virtual and in physical addresses, this can happen before the virtual address is translated to a physical address by the Translation Lookaside Buffer (TLB) or actual walking of the page tables (PT). After that, cache tags are compared to the actual, fully translated physical address to determine the correct entry [21]. As a consequence, this means that L1 cache relies on the actual, physical address of a memory location. If an attacker finds a way to poison this cache, other threads should see the modification when they access memory backed by the same physical address. This scenario happens quite often in modern

<sup>&</sup>lt;sup>1</sup>https://www.realworldtech.com/sandy-bridge/7/

operating systems. Shared libraries are commonly loaded into memory once and then mapped into the virtual address space of multiple processes. Since L1 cache is virtually-indexed and physically-tagged, poisoning the cache entries of such shared pages should also affect other processes since they are backed by the same physical addresses.

7.3. Hyper-Threading

On modern Intel CPUs, each physical core has its own L1 and L2 cache that is not shared with any of the other cores. Only L3 cache is shared between the cores of a single chip. This makes it more unlikely that the proposed vulnerability could occur in code running on different physical cores. As each of them has a unique L1 and L2 cache, the likelihood that changes made to memory during speculative execution could be visible on any of the other cores [9].

However, if CPUs support *Hyper-Threading* (HT), those caches are shared between two logical cores. Hyper-Threading is a technology developed by Intel to execute multiple logical threads on the same physical CPU. From the point of view of the operating system, the logical threads look like physical CPU cores. In the actual hardware however, two threads run on the same physical core which has some resources duplicated in order to allow for this behavior. For instance, each logical core has its own replicated set of registers. Other resources, such as certain buffers – which will be described in more detail later – are statically allocated between the two logical cores. There are also competitively-shared resources, including the cache hierarchy [9]. This means that during HT operation, both logical cores will share the same physical L1 and L2 caches. Taking this into account, it seems more likely that it might be possible to attack the sibling Hyper-Threading core with modifications made to caches during speculative execution.

7.4. Load and Store Buffers

While often ignored in literature for the sake of simplicity, reads and writes are actually not immediately serviced by the L1 cache even if they are contained therein. To further improve performance, Intel introduced load and store buffers. Writes are first queued into buffers and are not immediately committed to L1 cache. This allows to further improve performance by not having to wait for the cache write to complete but introduces a new problem. If the same memory location gets read again, the change might not be visible in the L1 cache yet. Consider the code in Listing 7.1.

Listing 7.1: reading modified data

mov [x], rax

mov rbx, [x]

The expected result would be that both RAX and RBX contain the same value once this code has been executed. However, if the modification made in the first instruction is only added to a buffer and not actually committed to L1 cache, the second instructions would read the old value and produce incorrect results. A simple workaround for this would be to stall the CPU until the buffer has been fully committed to the cache, however this would severely decrease performance in these situations. The solution implemented by Intel is called *store forwarding*. Reads will always first be satisfied from store buffers and only afterwards from the cache hierarchy. This complicates chip design but greatly simplifies software written for the CPU as the buffers become completely transparent to the programmer and do not have to be taken into account.

According to documentation provided by Intel [9], load and store buffers are statically allocated between two logical cores when Hyper-Threading is active and are not shared. In the context of our proposed attack vector, this means that writes only committed to buffers cannot be visible on other logical cores by hardware design.

# 7.5. Analysis of hardware design

To sum up the last chapters, there are two important pieces of information relevant to the practicality of the proposed attack. First, L1 cache entries are assigned at the level of physical addresses and are shared between logical cores when hyperthreading is active. From that point of view, changes made to L1 cache during speculative execution could very well be visible to other logical cores, if they are also undergoing speculative execution. The second important part is that writes are not directly applied to L1 cache but rather committed to a store buffer. To execute the proposed attack, it would be necessary to find a way to commit store buffer modifications to L1 cache during speculative execution but this seems to be prohibited by design.

A blog post from 2013 suggests that memory snapshotting is performed by using load and store buffers<sup>2</sup>. Modifications made during speculative execution are only ever written to store buffers which are then discarded if a roll back occurs. As described previously, this design would make our proposed attack impossible as these buffers are never shared between logical or physical cores.

<sup>&</sup>lt;sup>2</sup>https://fgiesen.wordpress.com/2013/03/04/speculatively-speaking/

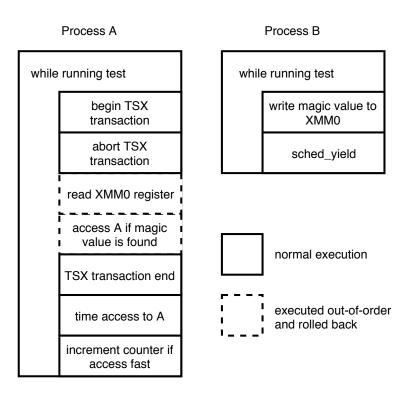

#### 7.6. Practical tests

We performed various tests to ensure that no detail has been overlooked where we attempted to see if modifications to an address made during speculative execution were visible on another core also undergoing speculative execution at any time. Our test setup included a thread that continuously changed the value of stored at an address during speculative execution without ever retiring the modification. A second thread simultaneously attempted to detect the magic value written by the first thread during speculative execution and leak the result through a cache side-channel. As expected by our analysis of the hardware design, we were unable to detect any modifications on the second core with statistically significant frequency.

#### 7.7. Conclusion

As demonstrated by both our analysis of the hardware specification as well as manually performed testing, we are reasonably certain that the proposed attack does not work with the hardware version we tested. It might be possible with other revisions, microcode or additional knowledge about undocumented parts of the Intel CPU but our setup does not seem vulnerable to the proposed attack. It is likely that Intel hardware is not vulnerable because of the way load and store buffers are split between Hypter-Threading cores.

# 8. Impact on other security boundaries

While being mostly known for breaking isolation between userland and kernel as well as between operating system processes, attacks based on the Meltdown and Spectre vulnerabilities have also been demonstrated to break other isolation schemes.

## 8.1. Software guard eXtension

SgxPectre [6] is a variant of the classical Spectre attacks that targets code running inside an Software Guard eXtension (SGX) enclave. This is especially worrisome considering that SGX has been specifically designed to allow for the creation of private memory regions that are protected from access even by code running with higher privileges.

An SGX secure enclave is an isolated execution environment that should provide both confidentially and integrity to the application inside, protecting it from all other software running on the system. Even before Spectre, researchers demonstrated that a cache side-channel could be established with a *Prime+Probe* attack in order to extract secret data from an enclave [22]. The SgxPectre attack takes this research a step further by poisoning branch targets used by the code inside the enclave. By carefully manipulating the branch target buffer with malicious code running on the same system, branches taken during execution of the enclave code can be influenced. As demonstrated by the researchers, secrets can then be leaked through selective cache loads, similar to traditional Spectre attacks.

## 8.2. System Management Mode

Researchers from Eclypsium implemented a Proof of concept <sup>1</sup> that showed how Spectre can also be used to read data from *system management RAM* (SMRAM). System management mode, sometimes referred to as Ring -2, is a high-privilege mode of operation on Intel CPUs that makes use of a dedicated memory region commonly referred to as SMRAM. After initial configuration during system boot, this

<sup>&</sup>lt;sup>1</sup>https://blog.eclypsium.com/2018/05/17/system-management-mode-speculative-execution-attacks/

memory region normally gets locked through dedicated hardware mechanisms and can then no longer be accessed, not even by the operating system kernel.

## 8.3. Conclusion

That both SGX and SMRAM are impacted by Spectre shows how far-reaching the effects of low-level architectural vulnerabilities can be. Both mechanisms were independently developed and designed to protect memory contents from all other software running on a system. Even though they worked on different principles, Spectre attacks can be used to break them without much customization.

# 9. The return branch predictor

The initial technical blogpost [17] the Google Project Zero team published on the Meltdown and Spectre attacks noted that there are three different branch prediction mechanisms in modern Intel CPUs. Two of these, the generic branch predictor and the specialized indirect call predictor, have been reverse engineered thoroughly by the Google Project Zero team and are described in detail in the blogpost. The third however, the return branch predictor, has not been analyzed in detail yet. The goal of the research conducted for this chapter was to reverse engineer the behavior and demonstrate the possibility of influencing the outcome of the return branch predictor on a Haswell CPU.

#### 9.1. Function-based control flow on x86

In order to be able to properly analyze the hardware-based features to improve performance of control flow based on function calls on the Intel architecture, it is first necessary to understand the process they are trying to improve.

Software often contains functionality that is required in multiple parts of the program. In order to decrease program size, it is desirable to reuse the same code rather than to store duplicates. The way this is generally handled in source code is the introduction of functions. From an abstract perspective, blocks of code are assigned a name and then referred to wherever needed. When a function is called, execution temporarily jumps to the code of the function and then resumes wherever it had been called from. In order to do this, it is necessary to keep track of the address where the function had been called from in order to be able to jump back there. The x86 architecture provides dedicated instructions to make this process faster and easier to implement. The CALL instruction is used to redirect execution flow to a function. It acts like a normal jump but additionally pushes the address after the CALL statement on the stack to store where execution will have to resume later. The stack is a specialized memory region dedicated mostly to temporary data such as local variables. When the function has completed, it executes the RET instruction which is typically the last instruction in every function. It pops the top-most value from the stack and resumes execution there. While CALL and RET are normally used in pairs, this behavior is not enforced. CALL simply jumps to the given location and pushes the return address on the stack while

RET takes whatever value is currently the top of the stack and jumps there.