# Long-Term Assessment of SRAM Physical Unclonable Functions on the ESP32

## Analysing RTC SLOW Memory for Building Secure IoT Authentication Systems

## Diploma thesis

for attainment of the academic degree of

Diplom-Ingenieur/in

submitted by

Christian Lepuschitz 51826356

in the

University Course Information Security at St. Pölten University of Applied Sciences

Supervision

Advisor: Dipl.-Ing. Dr. Henri Ruotsalainen

Assistance: -

## **Declaration**

Title: Long-Term Assessment of SRAM Physical Unclonable Functions on the ESP32

Type of thesis: <u>Diploma thesis</u>

Author: <u>Christian Lepuschitz</u> Student number: <u>51826356</u>

#### I hereby affirm that

- I have written this thesis independently, have not used any sources or aids other than those indicated, and have not made use of any unauthorized assistance.

- I have not previously submitted this thesis topic to an assessor for evaluation or in any form as an examination paper, either in Austria or abroad.

- this thesis corresponds with the thesis assessed by the assessor.

#### I hereby declare that

- I have used a Large Language Model (LLM) to proofread the thesis.

- ☑ I have used a Large Language Model (LLM) to generate portions of the content of the thesis. I affirm that I have cited each generated sentence/paragraph with the original source. The LLM used is indicated by a footnote at the appropriate place.

- □ no Large Language Model (LLM) has been used for this work.

Date Signature

## Kurzfassung

Durch die zunehmende Vernetzung von Geräten im Internet of Things (IoT)-Bereich steigen die Herausforderungen an deren Sicherheit. Trotz einer Vielzahl von Authentifizierungsmethoden basieren die meisten davon auf der Speicherung von Zugangsinformationen in nicht-flüchtigem Speicher. Im Falle einer physischen Kompromittierung von IoT-Geräten können solche Zugangsinformationen oftmals leicht gestohlen werden.

Static Random-Access Memory Physical Unclonable Functions (SRAM PUFs) bieten einen innovativen Ansatz zur Erzeugung von kryptografischen Schlüsseln. Sie basieren auf unregelmäßigen, submikroskopischen Herstellungsvariationen in SRAM-Speichern, die jedem produzierten Chip eine Art digitalen Fingerabdruck verleihen. Dieser Fingerabdruck ist für jeden Chip einzigartig, nicht klonbar und bietet daher ideale Voraussetzungen zur Authentifizierung von Geräten. Durch die Intra-Chip-Variabilität verändert sich dieser jedoch geringfügig zwischen jeder Verwendung, lässt sich durch externe Faktoren beeinflussen und weist zudem zeitliche Instabilität auf. Die Herausforderung besteht darin, trotz dieser Eigenschaften zuverlässige und sichere Authentifizierungssysteme zu entwickeln, ohne Zugangsinformationen am Gerät zu speichern.

In der vorliegenden Masterarbeit wird ein SRAM PUF basiertes Authentifizierungssystem für IoT-Geräte vorgestellt, welches speziell für den Einsatz am Mikrocontroller ESP32 getestet und entworfen wurde. Das entwickelte System unterscheidet sich von anderen in der Literatur vorgeschlagenen Authentifizierungssystemen primär in zwei Eigenschaften: Es nutzt ein Bit-Selection-Verfahren anstelle von Fehlerkorrekturverfahren und es setzt auf Application Programming Interface (API)-Keys anstelle von kryptografische Verfahren. Aufgrund des API-Key basierten Systems als zusätzlichen Faktor zu einer Mutual TLS (mTLS) basierten Authentifizierung, bietet dieses einen zusätzlichen Sicherheitsfaktor und lässt sich nahtlos in bestehende Authentifizierungssysteme einbinden.

Im Rahmen der Vorbereitungen wurden umfangreiche Langzeitmessungen durchgeführt, die Einflüsse verschiedener Umgebungstemperaturen und Spannungsversorgungen auf den SRAM evaluiert und die Unterschiede der uninitialisierten SRAM-Werte zwischen Microcontrollern derselben Serie sowie zwischen

verschiedenen Serien analysiert. Eine detaillierte Literaturrecherche bietet zudem einen umfassenden Überblick über das Internet of Things (IoT), PUF-Technologien mit speziellem Fokus auf SRAM PUFs sowie über Fehlerkorrekturverfahren.

Die Ergebnisse dieser Masterarbeit bieten eine solide Grundlage für zukünftige Forschungen und Entwicklungen im Bereich der SRAM PUF basierten Sicherheitsmechanismen.

## **Abstract**

With the rise of Internet of Things (IoT) devices, security challenges have increased. While various authentication methods exist, most of them rely on storing access information in non-volatile memory. However, if an IoT device is physically compromised, these credentials may be easily stolen.

Static Random-Access Memory Physical Unclonable Functions (SRAM PUFs) provide an innovative approach to generating cryptographic keys. They rely on the irregular sub-microscopic variations in SRAM to produce a unique digital fingerprint for each chip, making it impossible to copy and ideal for device authentication. However, due to intra-chip-variability, the fingerprint changes slightly with each use and can also be affected by external factors and temporal instability. Overcoming these challenges entails creating a secure and reliable authentication system without storing any access information on the device.

This master's thesis introduces an SRAM PUF-based authentication system for IoT, tested and designed specifically for the ESP32 microcontroller. Differing from other authentication systems proposed in the literature, this system uses a bit selection method instead of error correction methods and relies on Application Programming Interface (API) keys rather than cryptographic methods. The use of the API key-based system as an additional factor to Mutual TLS (mTLS) authentication provides an additional security factor and can be seamlessly integrated into existing authentication systems.

As part of the preparations, extensive long-term measurements were carried out. The influences of different ambient temperatures and power supplies on the SRAM were evaluated, and the differences in the uninitialised SRAM values between microcontrollers of the same series and between different series were analysed. A detailed literature review also provides a comprehensive overview of the IoT and Physical Unclonable Function (PUF) technologies, specifically focusing on SRAM PUFs and error correction methods.

The results of this master thesis provide a solid foundation for future research and development in SRAM PUF-based security mechanisms.

## **Contents**

| 1 | Intro | oductio  | on                                                | 1  |

|---|-------|----------|---------------------------------------------------|----|

|   | 1.1   | Contri   | bution                                            | 2  |

|   | 1.2   | Thesis   | Outline                                           | 2  |

|   | 1.3   | Limita   | tions                                             | 3  |

| 2 | Prei  | requisi  | tes                                               | 5  |

|   | 2.1   | Interne  | et of Things (IoT)                                | 5  |

|   |       | 2.1.1    | Use Cases                                         | 5  |

|   |       | 2.1.2    | Communication Protocols                           | 6  |

|   |       | 2.1.3    | Authentication Methods in IoT                     | 9  |

|   |       | 2.1.4    | Security Problems                                 | 10 |

|   |       | 2.1.5    | ESP32 Microcontroller                             | 12 |

|   | 2.2   | Physic   | al Unclonable Functions                           | 13 |

|   |       | 2.2.1    | Strong and Weak PUFs                              | 13 |

|   |       | 2.2.2    | Classification of PUFs                            | 14 |

|   |       | 2.2.3    | Types and Implementations                         | 14 |

|   |       | 2.2.4    | PUF Implementation: A Categorized Overview        | 15 |

|   | 2.3   | Error (  | Correcting Codes                                  | 17 |

|   |       | 2.3.1    | Applications of Error Correction                  | 18 |

|   |       | 2.3.2    | Error Correction in Physical Unclonable Functions | 19 |

|   | 2.4   | Static 1 | Random Access Memory (SRAM)                       | 19 |

|   |       | 2.4.1    | SRAM Based Physical Unclonable Functions          | 21 |

| 3 | Rela  | ated W   | ork                                               | 23 |

| - | 3.1   |          | ic ID                                             |    |

|   |       |          | Silicon Ageing                                    | 24 |

|   |      | 3.1.2  | SRAM Aging Mitigation (Anti-Ageing)                        | . 24 |

|---|------|--------|------------------------------------------------------------|------|

|   |      | 3.1.3  | Influence of Temperature Variation                         | . 24 |

|   | 3.2  | System | natic Bit Selection                                        | . 25 |

|   |      | 3.2.1  | Ramp Rate Impact on Reliability of SRAM PUF                | . 26 |

|   |      | 3.2.2  | Data Retention Voltage for Strong Cell Selection           | . 26 |

|   |      | 3.2.3  | Their Results                                              | . 26 |

|   | 3.3  | Vulner | rabilities of Memory-Based PUFs                            | . 27 |

|   |      | 3.3.1  | Mitigations                                                | . 28 |

|   | 3.4  | SRAM   | I PUF on the ESP32 Microcontroller                         | . 29 |

|   |      | 3.4.1  | Authentication System                                      | . 30 |

|   |      | 3.4.2  | ESP32 SRAM PUF Evaluation                                  | . 32 |

| _ |      |        |                                                            | 2.1  |

| 4 |      |        | ogy                                                        |      |

|   | 4.1  |        | rure Review                                                |      |

|   | 4.2  |        | ating Suitable Microcontrollers                            |      |

|   | 4.3  |        | rements and Analysis                                       |      |

|   | 4.4  | Implen | menting an Authentication System                           | . 38 |

| 5 | Setu | qı     |                                                            | . 41 |

|   | 5.1  | Config | guring the Development Environment                         | . 41 |

|   | 5.2  | Develo | opment of a Firmware to Read Uninitialised SRAM PUF Values | . 42 |

|   |      | 5.2.1  | Reading Internal SRAM 0                                    | . 43 |

|   |      | 5.2.2  | Reading Internal SRAM 1                                    | . 44 |

|   |      | 5.2.3  | Reading Internal SRAM 2                                    | . 44 |

|   |      | 5.2.4  | Reading RTC FAST Memory                                    | . 45 |

|   |      | 5.2.5  | Reading RTC SLOW Memory                                    | . 45 |

|   | 5.3  | Measu  | rement Server                                              | . 46 |

|   |      | 5.3.1  | Network                                                    | . 46 |

|   |      | 5.3.2  | Authentication                                             | . 46 |

|   |      | 5.3.3  | Database                                                   | . 46 |

|   |      | 5.3.4  | Endpoints                                                  | . 47 |

|   |      | 5.3.5  | Deployment                                                 | . 48 |

|   |      |        |                                                            |      |

| 6  | Mea   | suring  | and Analysing the SRAM                                     | <b>4</b> 9 |

|----|-------|---------|------------------------------------------------------------|------------|

|    | 6.1   | SRAM    | I PUF Measurements                                         | 49         |

|    |       | 6.1.1   | Long-Term Measurements                                     | 52         |

|    |       | 6.1.2   | Power Measurements                                         | 52         |

|    |       | 6.1.3   | Overwriting the Start-Up Values                            | 53         |

|    |       | 6.1.4   | Testing the Effects of Temperature                         | 53         |

|    | 6.2   | Analys  | sing and interpreting the data                             | 53         |

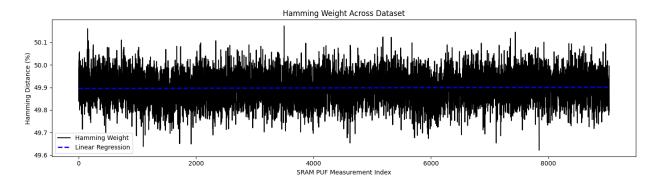

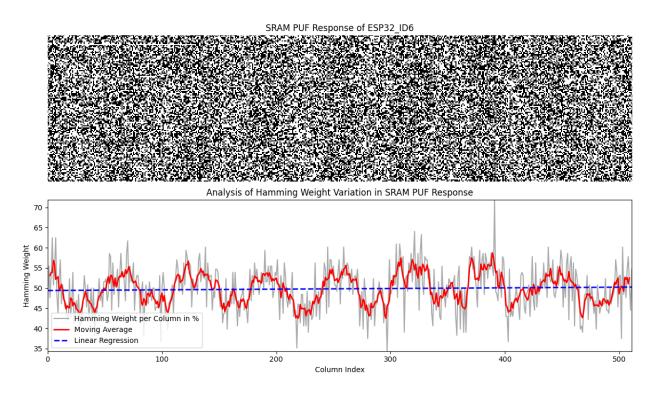

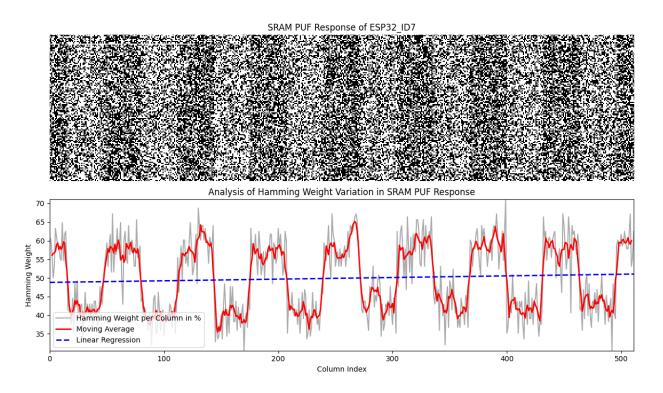

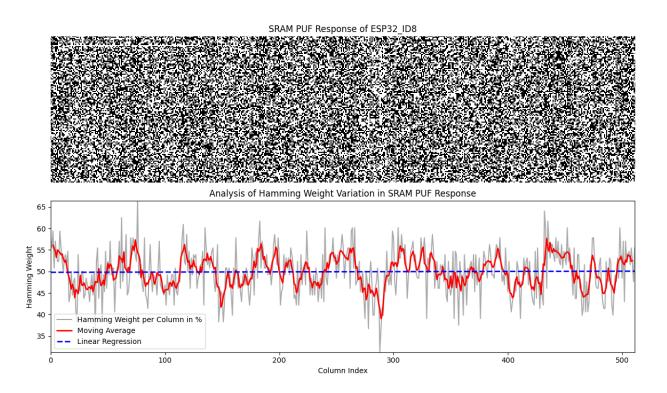

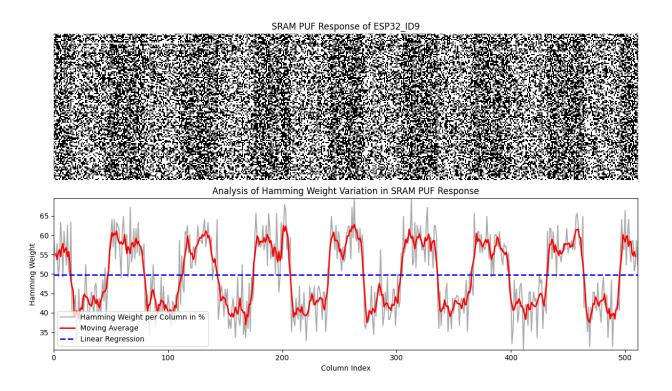

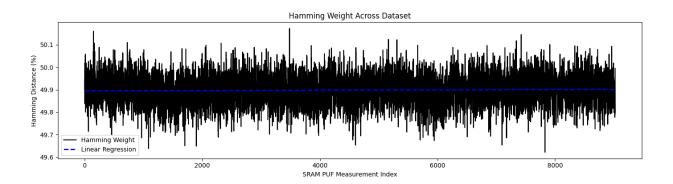

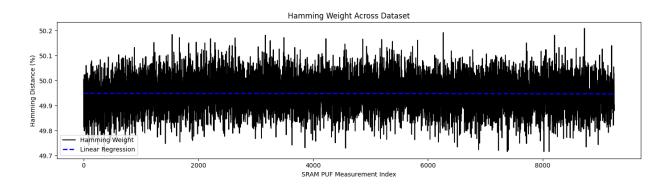

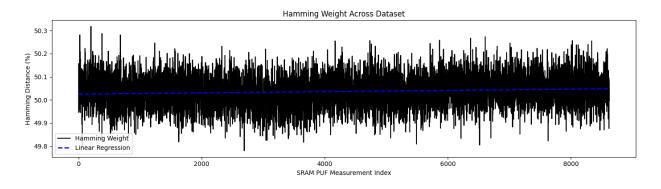

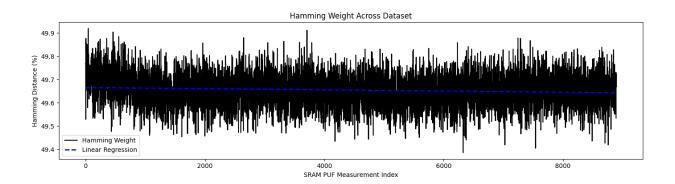

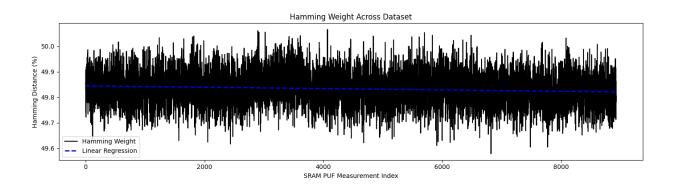

|    |       | 6.2.1   | Hamming Weight                                             | 55         |

|    |       | 6.2.2   | Normalised Hamming Distance and Hamming Similarity         | 56         |

|    |       | 6.2.3   | Long-Term Bit Stability Evaluation                         | 58         |

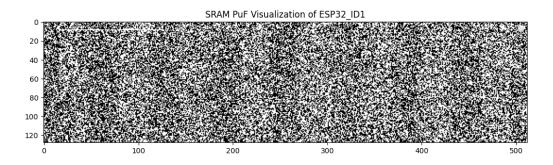

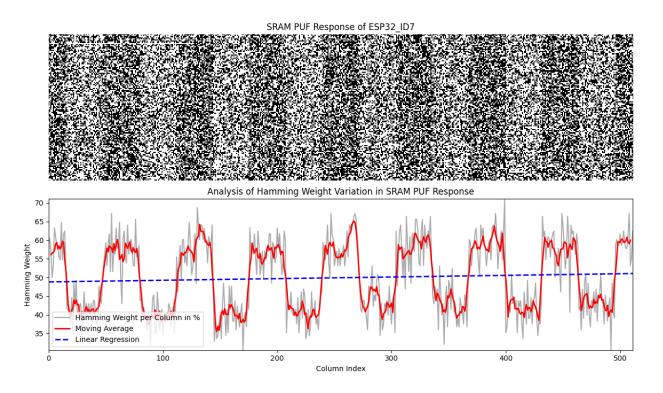

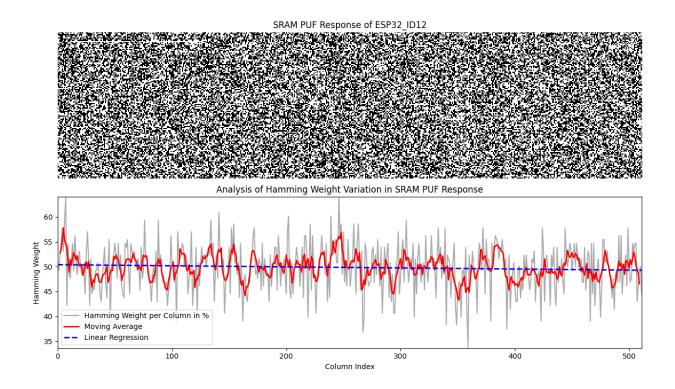

|    |       | 6.2.4   | Visualising SRAM                                           | 60         |

|    |       | 6.2.5   | Examining Variations in Power Supply Voltages              | 64         |

|    |       | 6.2.6   | Examining Ambient Temperature Variations                   | 66         |

| 7  | lmp   | lement  | ing an Authentication System                               | 67         |

|    | 7.1   | Conce   | pt                                                         | 67         |

|    | 7.2   | Impler  | mentation                                                  | 68         |

|    |       | 7.2.1   | Generating the PUF Challenge and the API Key               | 68         |

|    |       | 7.2.2   | Development and Configuration of the Authentication Server | 69         |

|    |       | 7.2.3   | Authenticating the ESP32                                   | 70         |

|    |       | 7.2.4   | Testing                                                    | 75         |

| 8  | Cor   | nclusio | n                                                          | 77         |

|    | 8.1   | Future  | Work                                                       | 78         |

| Li | st of | Figure  | S                                                          | 81         |

| Li | st of | Tables  |                                                            | 82         |

| Αd | crony | ms      |                                                            | 85         |

| Bi | bliog | ıraphy  |                                                            | 91         |

| Α  | App   | endix   | Visualisations                                             | 99         |

|    | A.1   | SRAM    | Visualisations                                             | 99         |

| В | Арр | endix Source Code                | 115 |

|---|-----|----------------------------------|-----|

|   | A.4 | Hamming Weight Across Dataset    | 112 |

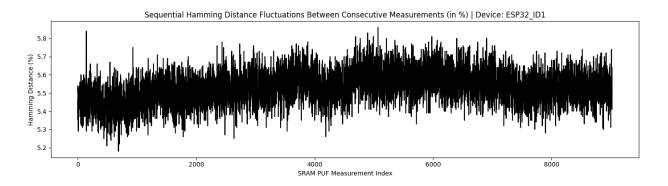

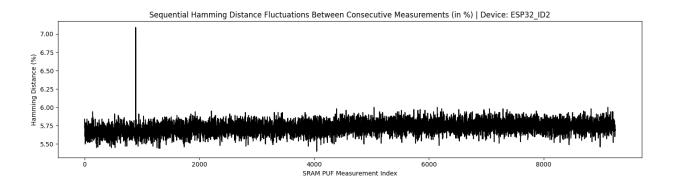

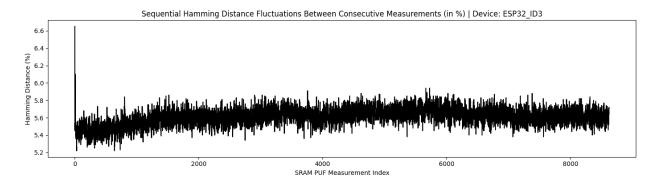

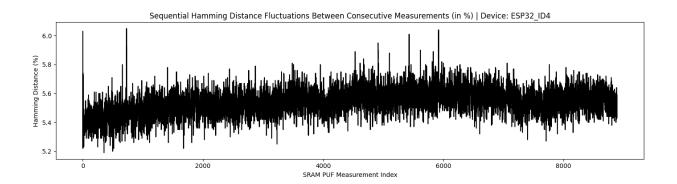

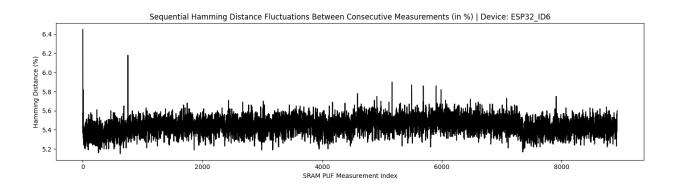

|   | A.3 | Consecutive Hamming Distances    | 110 |

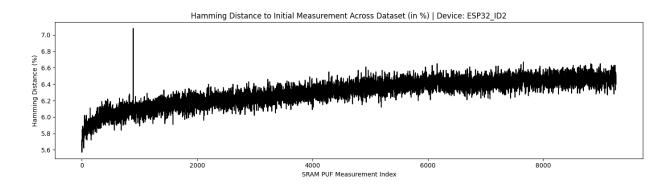

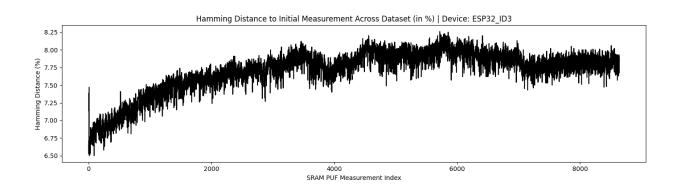

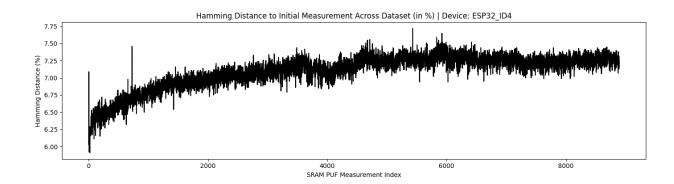

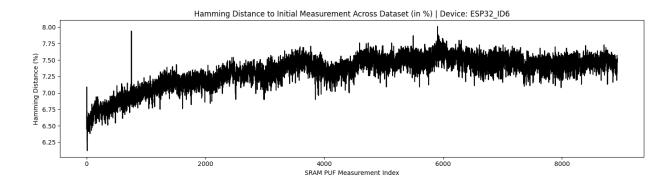

|   | A.2 | Hamming Distances Across Dataset | 108 |

|   |     |                                  |     |

## 1. Introduction

Static Random-Access Memory Physical Unclonable Functions (SRAM PUFs) offer a promising approach to secure authentication of Internet of Things (IoT) devices. They are based on the uniqueness of SRAM memories, which results from sub-microscopic manufacturing variations. As soon as an SRAM memory receives power, each cell in the SRAM assumes a state of either 0 or 1. Theoretically, the probability for both cases is 50%, but due to minute production differences at the atomic level, certain cells tend to be 0, and other cells tend to be 1. Other cells are volatile and change their value whenever switched on. If a large part or the entire SRAM memory is now read out in an uninitialised state, this results in a pattern of 0's and 1's, which is very similar for every SRAM memory with every measurement but completely different to the patterns of other SRAM memories. These properties cannot be technically copied, which is why they are considered a Physical Unclonable Function (PUF). Due to their properties, SRAM PUFs offer good prerequisites for creating a hardware-based digital fingerprint and, thus, uniquely identifying and authenticating devices.

SRAM PUFs are a popular research topic and are used in various industries such as aerospace, defence, medical equipment, and IoT [1]. Research in this field mainly concentrates on analysing dedicated SRAM memories, developing methods for costly Field Programmable Gate Arrays (FPGAs), and designing cryptographic authentication methods that necessitate special server software. In recent years, there has also been increasing research into the feasibility of implementation for standard microcontrollers in IoT devices. Nevertheless, there still needs to be more easy-to-implement solutions for the masses. This master's thesis aims to close this gap and develop an easy-to-implement procedure that can be seamlessly integrated into existing authentication systems without server-side adaptations.

#### 1.1. Contribution

As part of this work, extensive measurements were carried out on several ESP32 microcontrollers, confirming them as good candidates for an SRAM PUF-based authentication method. The effects of silicone ageing on several microcontrollers were analysed as part of automated long-term measurements. Subsequent manual tests analysed the influence of external factors, such as the ambient temperature and a variable power supply, on the stability of the PUFs. Furthermore, the distribution of 0's and 1's in each tested ESP32's memory was evaluated, and the differences between all microcontrollers used were evaluated. The results provide an in-depth insight into the characteristics of the SRAM used and can be used by future research as a basis for SRAM PUF procedures on the ESP32.

In addition, a simple authentication system was proposed that can derive a large number of different API keys using SRAM PUF. This allows IoT devices to be authenticated to server systems without storing access information locally. Suppose attackers manage to clone the firmware and install it on identical microcontrollers. In that case, they cannot authenticate themselves, as the SRAM memories differ from the original system at an atomic level.

#### 1.2. Thesis Outline

This thesis is divided into several chapters, which can be roughly subdivided into a theoretical and a practical part. Chapters 1 to 3 cover the theoretical part, while chapters 4 to 7 focus on the practical part.

- 1. **Introduction:** provides a general overview of the research subject and introduces the topic in more detail

- 2. **Prerequisites:** This chapter deals with the basics necessary to understand the present work. Specifically, it is dedicated to the Internet of Things (IoT), Physical Unclonable Functions (PUFs), Error Correcting Codes (ECCs) Static Random-Access Memory (SRAM).

- 3. **Related Work:** This chapter provides an overview of research in this area and presents some selected papers in more detail. The papers mentioned serve as a basis for the selected test procedures and the design of the proposed authentication system.

- 4. Methodology: This chapter explains the structure of this master thesis in detail. It explains how the selection of the microcontrollers took place, how the measurements and subsequent analyses were carried out, and based on which decisions the proposed authentication system is now available in its current form.

- 5. **Setup:** This chapter describes the setup of the development environment, firmware writing for microcontrollers, and data storage.

- 6. Measuring and Analysing the SRAM: This chapter is dedicated to the structure of the measurements and the analysis of the SRAM. It describes how the microcontroller was programmed, how the SRAM was read out, how the data was stored during the long-term measurements and how the collected data was finally analysed.

- 7. **Implementing an Authentication System:** This chapter covers the technical implementation of the authentication system. It explains how the bits are selected, how a key is derived from them, what a simple HTTP authentication server might look like and how the devices are authenticated via an encrypted connection.

- 8. **Conclusion:** At the end of the paper, the results of the analyses are briefly summarised, and the authentication system is explained again.

- 9. **Appendix Visualisations:** This part contains a part of the measurements carried out and the source code written to evaluate the measurements and the authentication system.

#### 1.3. Limitations

The authentication system developed was tested for functionality but not analysed in terms of security. For this reason, it should only be used for testing purposes or for further research. In Section 8.1, some potential research topics are suggested that could enhance the security of this system.

## 2. Prerequisites

This chapter provides a comprehensive overview of the following topics: Internet of Things (IoT) [Section 2.1], Physical Unclonable Functions (PUFs) [Section 2.2], Error Correcting Codes (ECCs) [Section 2.3], and Static Random-Access Memory (SRAM) [Section 2.4].

#### 2.1. Internet of Things (IoT)

The Internet of Things (IoT) refers to a network of physical objects devices, vehicles, appliances, buildings, and other itemsembedded with sensors, software, and other technologies to connect and exchange data with other devices and systems over the internet [2]. These devices, often called "smart" devices, can collect, send, and act on data they acquire from their environments [3]. IoT applications range from consumer products like smart home devices (thermostats, lighting systems, security cameras) and wearable technology to industrial and infrastructure applications such as smart cities, smart grids, and advanced manufacturing. <sup>1</sup> In IoT, several options exist to transmit data, including Wi-Fi, Bluetooth, satellite and Long Range Wide Area Network (LoRaWAN) [4] [5]. With the use of internet connectivity and wireless transmission technologies, various sources of information, such as sensors, smartphones, and cars, are becoming increasingly interconnected. The number of internet-enabled devices is - seemingly exponentially - increasing [6].

#### 2.1.1. Use Cases

Intelligent networking and data analysis are enabling IoT to revolutionize the way we work in a wide variety of areas, making work more efficient and autonomous.

In **agriculture**, IoT helps develop the supply and growth of crops by obtaining information about the environment through various sensors. In the **food** industry, air quality and oxygen sensors ensure the safety

<sup>&</sup>lt;sup>1</sup>Generated by GPT-4

of workers. In the meat processing industry, IoT monitors ozone levels to ensure the safety and quality of products.

In **healthcare**, IoT systems monitor the health status of patients and generate alerts if necessary. Nursing staff can thus use networked systems to remotely monitor patients with a wide range of disorders such as diabetes, dementia, Alzheimer's and others.

In urban areas, IoT systems are used to **optimize traffic flow**. For example, city buses are monitored using GPS and time information to provide a city-wide overview of current traffic conditions and forecasts of arrival times, transit times and congestion routes on digital maps.

Industry, transport and business are not the only areas in which IoT systems are used; they are also used in a wide range of **smart home** devices. Through a combination of sensors and intelligent systems, everyday objects are connected in a network to communicate and solve problems without human intervention. [6]

#### 2.1.2. Communication Protocols

Depending on their type and use, IoT systems communicate with various protocols. The choice of the network protocol used depends on various factors, such as the location where the IoT system is operated, the amount of data to be transmitted, power consumption (especially in battery operation), the size of the network and the available frequency bands (which may differ from country to country). Equally important is the distance over which the data is transmitted. Network protocols such as Sigfox or Cellular, used in smart grid systems or for controlling street lighting, are particularly suitable for long-distance data transmission (up to 50 km). Data rates for protocols designed for long distances, such as Sigfox, are generally rather low (100-600bps), and the power consumption is considerably higher [7].

Network protocols with higher transmission rates but shorter distances include Bluetooth, ZigBee and IPv6 over Low power Wireless Personal Area Network (6LoWPAN). These three, especially the latter, are characterized by very low power consumption and thus enable battery operating times of 1-2 years [7].

Although Near Field Communication (NFC) and Radio Frequency Identification (RFID) are used in IoT systems, they only work over very short distances and can only transmit a small amount of data. RFID tags can be used either actively or passively (with or without an embedded battery). However, the data stored

on a RFID tag is static and cannot be used for transmitting changing data, such as measurements. Although NFC works similarly to RFID, it is designed for even shorter distances and uses a two-way communication system [7].

Which network protocol is most suitable for an IoT system, consequently, depends on the following factors

- · Available frequency band

- Energy efficiency

- · Required data rate

- Required range

- Security (encryption)

- Scalability

Just like network protocols, application protocols have their advantages and disadvantages. In the following, however, only Internet Protocol (IP)-based protocols are described. The most commonly used IoT protocols include Constrained Application Protocol (CoAP), Extensible Messaging and Presence Protocol (XMPP), representational state transfer (REST)ful Hypertext Transfer Protocol (HTTP), Message Queuing Telemetry Transport (MQTT), WebSocket, Advanced Message Queuing Protocol (AMQP) and Data Distribution Service (DDS). Contrary to the Transmission Control Protocol (TCP)-based protocols, CoAP and DDS are based on User Datagram Protocol (UDP), making them the most lightweight protocols [8].

[8] outlines the advantages and disadvantages of the protocols mentioned as follows:

#### CoAP:

- Advantages: It supports multicast, has low overhead, and minimizes the complexity of mapping with HTTP.

- **Disadvantages**: It does not enable communication layer security, and there are few existing libraries and solution support.

#### XMPP:

- Advantages: Flexibility of communication models, low latency, real-time, easy to understand, and extend; any XMPP server can be isolated.

- Disadvantages: Heavy data overhead and, therefore, not suitable for embedded IoT applications.

#### **RESTful HTTP:**

- Advantages: Easy application maintenance and no client state management on the server.

- **Disadvantages**: The client must store all data needed to perform a query locally, there is no error handling, and it is difficult to extend.

#### **MQTT:**

- Advantages: It is useful for remote site connections, is easy to implement, has a small code footprint, is lightweight, and uses an asymmetric client-server relationship.

- **Disadvantages**: Basic message queuing implementations, no error-handling, does not address connection security, and extensions are hard to add.

#### WebSocket:

- Advantages: Simplifies web communication and co-network compatibility and offers connection management.

- **Disadvantages**: It has specific hardware requirements and does not offer useful open-source implementations targeted at embedded systems.

#### **AMQP:**

- Advantages: It is an International Organization for Standardization (ISO) standard that provides complex message queuing implementations, high routing reliability, and security, is easily extensible, and has a symmetric client-server relationship.

- **Disadvantages**: It has a larger packet size than other protocols and does not support Last Value Queue (LVQ).

#### DDS:

• Advantages: It enables real-time monitoring of quality of service, features a decentralized architecture, and allows dynamic detection of senders and subscribers.

#### 2.1.3. Authentication Methods in IoT

The authentication procedures for IoT systems differ from traditional authentication methods in that device authentication is used instead of user authentication. This means that the identity of a user is not checked interactively, but the device itself confirms its identity to other participants or servers. Although device authentication is also used in classic IT systems, there are some particular difficulties regarding IoT authentication. These include limited resources, connection security (often wireless) and scalability.

In the following, the authentication methods such as OTP, Certificate Based Authentication (CBA), Identity Management (IDM), Biometry and Physical Unclonable Function (PUF) are briefly explained based on the results of a literature search in [9]:

- One Time Password (OTP) based authentication methods [10] rely on pairing techniques facilitated by elliptic curves. The generation occurs in four phases: setup, extraction, generation and validation. In the first phase, a pair of prime numbers is generated, and in the second phase, IoT applications and devices register with the Private Key Generator (PKG) and receive private and public keys. In the third phase, the application requests data from the IoT device, and the PKG automatically generates the key of the requesting device. During validation in the fourth phase, the application and the IoT device exchange data via the OTP. The IoT device checks whether the OTP originates from the application and performs the requested task. This method for generating the OTP is based on the Lamport algorithm. [9]

- Certificate Based Authentications (CBAs) offer a secure approach to authenticating IoT devices. Certificates are issued to IoT devices by a central certification authority, as is common in a classic Public Key Infrastructure (PKI) infrastructure. Entities that issue certificates and entities that are responsible for authentication are strictly separated. The Datagram Transport Layer Security (DTLS) handshake protocol is used to authenticate IoT devices on the server, as proposed in [11]. However, the DTLS handshake protocol is only available without restrictions on IoT systems with sufficient Random-Access Memory (RAM) and Read-Only Memory (ROM). These resources are often limited on IoT devices where the DTLS protocol is, therefore, not entirely usable. [9]

- Identity Management (IDM) based procedures [12] provide authorization and authentication for IoT users. Using a key-based authentication method, it provides single sign-on to IoT devices. An

Identity Provider (idP) manages users' identity and authentication characteristics and thus provides the required credentials for systems. This system enables a non-interactive login and provides identity checks based on private keys, which have proven to be more secure than passwords. [9]

• **Biometric** authentication systems use a person's unique physical characteristics, such as their iris, fingerprint, heartbeat, or voice, to verify their identity. Although these systems are relatively new to the field of IoT, they have the potential to protect personal IoT devices from theft. This is achieved by allowing only the owner, who has confirmed their identity using biometric features, to access the device. Biometric authentication is particularly useful for devices like personal fitness trackers with limited input options. Moreover, it can be used for authentication in other areas, such as unlocking/locking cars, homes or bank accounts. [13]

An alternative approach to the classic approaches mentioned above is using Physical Unclonable Functions. This concept is explored in detail in a dedicated chapter of this thesis. In essence, the PUF approach generates a key from a device's unique physical characteristics, safeguarding against the risks of compromise through counterfeiting or cloning of IoT systems.

#### 2.1.4. Security Problems

IoT devices face a variety of different security issues. This chapter provides a detailed overview of security issues in IoT systems and explains methods to address these security threats. This chapter is based on findings and recommendations from [14], which provides a comprehensive analysis of the security landscape in the IoT sector.

- **Deficient physical security:** IoT devices are primarily operated in unmonitored environments, making them susceptible to unauthorized access and control by attackers with minimal effort. This vulnerability allows for inflicting physical damage, exposing implemented cryptographic systems, or replicating the device's firmware.

- **Insufficient energy harvesting:** By default, IoT systems can not renew their energy. Attackers can carry out targeted attacks on IoT systems to consume the stored energy and render the systems unusable for regular operation.

- Inadequate authentication: Due to the limited resources of IoT systems, implementing secure authentication mechanisms poses a significant challenge. Attackers can attack weak authentication systems, thus jeopardising data integrity. The authentication keys used are at permanent risk of being lost, destroyed or damaged. If the keys are not securely stored or transmitted, authentication systems may not be sufficient to ensure data integrity.

- Improper encryption: Due to resource limitations in IoT systems, encryption mechanisms are not always implemented with sufficient robustness. It is often possible for attackers to bypass the implemented encryption mechanisms and gain access to sensitive information.

- Unnecessary open ports: Many IoT devices have open ports that are not intended to be accessible from the internet. These include, for example, services used to manage or maintain these devices. These services are often not adequately protected, making them vulnerable to attacks.

- Insufficient access control: Numerous manufacturers of IoT systems have not implemented strong password policies and deliver devices with default credentials. Users often do not change these default credentials, providing a target for various attacks. In addition, users with elevated rights often use the default credentials.

- Improper patch management capabilities: Regular security updates and patches should be provided to ensure the secure operation of IoT systems. In many cases, manufacturers do not regularly provide security updates, or there are no automatic update mechanisms to keep the devices up to date. Even if automatic update mechanisms are in place, integrity checks are often not in place, making IoT devices vulnerable to fake, malicious updates.

- Weak programming practices: Many products in the IoT sector do not adhere to common programming and security practices, which can lead to vulnerabilities. For example, numerous products are delivered with known vulnerabilities, such as backdoors and root users as the main access point. Furthermore, Secure Socket Layer (SSL) is not always utilised, meaning that data is transmitted in plain text and can be read by external parties. Attackers can exploit these vulnerabilities to obtain and modify data and gain unauthorised access to systems, among other malicious activities.

• **Insufficient audit mechanisms:** Logging and auditing procedures are usually not used in the IoT environment for various reasons. As a result, detection and response in the event of an attack are difficult or even impossible.

#### 2.1.5. ESP32 Microcontroller

The ESP32 from Espressif Systems [15] is a versatile and powerful microcontroller used in various applications like smart homes, wearable electronics and industrial automation. It offers a multitude of features, including Wi-Fi and Bluetooth connectivity, a dual-core processor, a wide range of General Purpose Input/Output (GPIO) pins, and support for various communication modes, making it ideal for IoT projects. It can withstand operating temperatures ranging from -40°C to +125°C degrees (depending on the exact model) and has a very low power consumption (10μA in deep sleep mode), perfect for use in remote locations without a continuous power supply.

Besides numerous standard features, the ESP32 also has dedicated security features. These include [15]

- Secure boot

- Flash encryption

- 1024-bit One Time Password (OTP), up to 768-bit for customers

- Cryptographic hardware acceleration:

- Advanced Encryption Standard (AES)

- Hash (Secure Hash Algorithm 2 (SHA-2))

- Rivest-Shamir-Adleman (RSA)

- Elliptic Curve Cryptography (ECC)

- Random Number Generator (RNG)

Due to the wide range of possible applications, the economically attractive price, the widespread use in a wide range of products and the presence of safety functions, this microcontroller was chosen for the subject of this master's thesis.

#### 2.2. Physical Unclonable Functions

Today's Information Technology (IT) systems use digital keys to protect confidential information and identities and guarantee authenticity. These digital keys form the basis for the cryptographic protocols used today. While the cryptographic protocols are public and can be viewed by anyone, the digital key (private key) must be kept secret. In traditional IT systems, the digital keys are usually stored in Non Volatile Memories (NVM) (such as those used in Trusted Platform Modules (TPMs)). The secure storage of cryptographic keys over a prolonged period of time poses a significant difficulty, especially if NVMs do not have a dedicated protection mechanism. The keys could, therefore, be read and the security of a system could be jeopardized.

In addition to the storage of cryptographic key material in NVMs, there are other options, such as the use of Hardware Security Modules (HSMs) or storage in the cloud [16]. An alternative approach to storage is offered by so-called Physical Unclonable Functions (PUFs). PUFs use inherent, random variations in the hardware resulting from minimal production deviations to generate secret key material [17]. These minimal variations vary from device to device but are always unique, similar to fingerprints. Although it is possible to measure the random variations, creating an exact physical copy remains impractical [17].

The use of PUFs is usually very cost-effective and does not affect the function of Integrated Circuits (ICs).

PUFs must meet the following requirements [18]:

- robust (they should not change over time)

- unique (they must be different from device to device)

- easy to test

- difficult or impossible to replicate

- difficult or impossible to predict.

#### 2.2.1. Strong and Weak PUFs

The strength of PUFs is usually divided into the categories **strong** and **weak**. Weak and strong PUFs differ in the number of Challenge Response Pairs (CRPs) that can be generated by a single device and the ratio in which they increase with increasing device size. Weak PUFs scale worse (linear or polynomial) than strong PUFs (exponential).

If an attacker gains physical access to a PUF, they can read all possible CRPs, while it is not possible to copy the physical PUF itself. With a strong PUF, on the other hand, it is not possible for an attacker to read all CRPs. Even if an attacker has access to the PUF and reads out many CRPs, the probability that he will later be able to solve a challenge with it is negligible. [18]

#### 2.2.2. Classification of PUFs

There are many different approaches to implementing PUFs; [18] divides them into different levels using an organic system, including application, randomness, source, family and concept. Applications are divided into "All Electronic", where the PUF is directly integrated into the electronics, and "Hybrid", where external sources such as external light sources may be used.

#### Implicit (Intrinsic) and Explicit (Extrinsic) PUFs

The source of randomness (randomness source) can be categorized into two types: implicit (intrinsic) and explicit (extrinsic). PUFs with implicit evaluation possess inherent randomness, which is evaluated internally. The mechanisms for validating the PUF are, therefore, embedded directly into the device. Further processing, such as hashing, can occur without the PUF response being externally accessible. Implicit assessments are, therefore, more resistant to MITM and side-channel attacks and tend to be more accurate, easier to use and less susceptible to interference from attackers.

In contrast, explicit PUFs do not have an integrated source of randomness integrated into the device but are located externally. The validation of the PUF (after the measurement) is therefore conducted externally to the device. [18]

#### 2.2.3. Types and Implementations

PUFs are divided into different families, categorized based on their functionality [18]. The categories are:

- Racetrack (analyses system latency by measuring signal completion time through wiring or components. They operate in the time domain and are similar to transient/glitch PUFs, but they differ in signal propagation examination) [19] [20] [21]

- Transient/Glitch (evaluate temporary signals emitted by circuits. Combining several ring oscillators and XORing them generates distinctive patterns, which are used to identify transient errors in signal inputs or correct any temporary glitches in intricate circuit functions) [22] [23]

- Direct Characterization (involves direct characterisation of electronic components without additional fabrication steps. Properties such as current response to voltage, capacitance, or circuit interconnect are examined) [24] [25] [26] [27]

- Volatile Memory (utilise unit cell properties to derive responses, including examining SRAM and DRAM reactions) [28] [29] [30] [31]

- Non Volatile Memory (store data without constant power using resettable cell property. They create random patterns with modified writing signals, acting as a random number generator and storage for a random key) [32] [33] [34]

- Radio Frequency (assess radio-frequency radiation interaction with objects for randomness. Some RFID systems use all-electronic PUFs without radiofrequency evaluation) [35] [36]

- Optical (uses visible light interacting with a random microstructure to create unpredictable patterns.

The original form involves shining a laser through a plate with refractive particles for pattern analysis) [37] [38] [39] [40] [41]

- Magnetic (explores the magnetic field surrounding an object to investigate the inherent randomness during manufacturing)[42]

Some of these categories are further subdivided into Time Domain PUFs (including Racetrack and Transient/Glitch), Memory Cell PUFs (including Volatile Memory and Non Volatile Memory) and Optical PUFs (Implicit and Explicit). [18]

#### 2.2.4. PUF Implementation: A Categorized Overview

An overview of various PUF implementations, including assignment to applications, randomness source and family, was taken from [18] and split into two different tables: **All Electronic** (Table 2.1) and **Hybrid** (Table 2.2).

#### 2. Prerequisites

| Application    | Randomness Source | Family                  | Concept                                           |

|----------------|-------------------|-------------------------|---------------------------------------------------|

| All Electronic | Implicit          | Racetrack               | Ring Oscillator PUF                               |

| All Electronic | Implicit          | Racetrack               | Arbiter PUF                                       |

| All Electronic | Implicit          | Racetrack               | Clock PUF                                         |

| All Electronic | Implicit          | Transient/Glitch        | Glitch PUF                                        |

| All Electronic | Implicit          | Transient/Glitch        | Transient Effect Ring Oscillator (TERO) PUF       |

| All Electronic | Implicit          | Direct Characterisation | Threshold Voltage (TV)-PUF                        |

| All Electronic | Implicit          | Direct Characterisation | Power Distro. PUF                                 |

| All Electronic | Implicit          | Direct Characterisation | Cellular Neural Network (CNN) PUF                 |

| All Electronic | Implicit          | Direct Characterisation | Vertical Interconnect Access (VIA) PUF            |

| All Electronic | Implicit          | Direct Characterisation | QUALPUF                                           |

| All Electronic | Implicit          | Volatile Memory         | SRAM PUF                                          |

| All Electronic | Implicit          | Volatile Memory         | Bistable Ring PUF                                 |

| All Electronic | Implicit          | Volatile Memory         | MEmory Cell-based Chip Authentication (MECCA) PUF |

| All Electronic | Implicit          | Volatile Memory         | SRAM Failure PUF                                  |

| All Electronic | Implicit          | Volatile Memory         | Dynamic Random Access Memory (DRAM) PUF           |

| All Electronic | Implicit          | Volatile Memory         | Rowhammer PUF                                     |

| All Electronic | Explicit          | Non Volatile Memory     | Memristor PUF                                     |

| All Electronic | Explicit          | Non Volatile Memory     | Phase change key generator (PCKGen)               |

| All Electronic | Explicit          | Non Volatile Memory     | Spin-Transfer-Torque Magnetic RAM (STT-MRAM) PUF  |

| All Electronic | Explicit          | Direct Characterisation | Accoustical PUF                                   |

| All Electronic | Explicit          | Direct Characterisation | Coating PUF                                       |

| All Electronic | Explicit          | Direct Characterisation | Super High Information Content (SHIC) PUF         |

| All Electronic | Explicit          | Direct Characterisation | Micro-Electrico-Mechanical System (MEMS) PUF      |

| All Electronic | Explicit          | Direct Characterisation | Carbon Nanotube (CN) PUF                          |

| All Electronic | Explicit          | Direct Characterisation | Board PUF                                         |

| All Electronic | Explicit          | Direct Characterisation | Quantum Electronic PUF (Q-EPUF)                   |

| All Electronic | Explicit          | Direct Characterisation | Self-Assembly PUF                                 |

| All Electronic | Explicit          | Direct Characterisation | Nano-Electrico-Mechanical System (NEMS) PUF       |

Table 2.1.: All Electronic PUF implementations

| Application | Randomness Source | Family          | Concept                                         |

|-------------|-------------------|-----------------|-------------------------------------------------|

| Hybrid      | Explicit          | Radio Frequency | Radio-Frequency DNA (RF-DNA) PUF                |

| Hybrid      | Explicit          | Radio Frequency | LC (Inductor [symbolized by L] - Capacitor) PUF |

| Hybrid      | Explicit          | Optical         | Optical PUF                                     |

| Hybrid      | Explicit          | Optical         | Phosphor PUF                                    |

| Hybrid      | Explicit          | Optical         | Nanowire Distro. PUF                            |

| Hybrid      | Explicit          | Optical         | Optical Fibre PUF                               |

| Hybrid      | Explicit          | Optical         | Nanoparticle Distro. PUF                        |

| Hybrid      | Explicit          | Optical         | Liquid Crystal PUF                              |

| Hybrid      | Explicit          | Optical         | Quantum Optical PUF (Q-OPUF)                    |

| Hybrid      | Explicit          | Optical         | Monolayer Depo. PUF                             |

| Hybrid      | Implicit          | Optical         | Paper PUF                                       |

| Hybrid      | Implicit          | Optical         | Compact Disk (CD) PUF                           |

| Hybrid      | Implicit          | Magnetic        | Magnetic PUF                                    |

Table 2.2.: Hybrid PUF implementations

According to [18], the most important representatives of the PUFs mentioned above include

- Ring Oscillator PUFs (Intrinsic / Racetrack)

- Arbiter PUF (Intrinsic / Racetrack)

- Threshold Voltage (TV)-PUF (Intrinsic / Direct Characterization)

- Power Distro. PUF (Intrinsic / Direct Characterization)

- Vertical Interconnect Access (VIA) PUF (Intrinsic / Direct Characterization)

- Static Random-Access Memory (SRAM) PUF (Intrinsic / Volatile Memory)

- Quantum Optical PUF (Q-OPUF) (Explicit / Optical)

## 2.3. Error Correcting Codes

Wherever digital information is processed, stored or transmitted, errors can occur. Individual bits can change their value from 0 to 1 or vice versa, rendering data unusable or compromising data integrity. Error correction codes were developed to correct these errors and improve the reliability of data transmission and storage [43].

As early as the 1940s, Claude Shannon [44] showed in a theorem that nearly error-free communication is possible via a noisy channel. Redundancy is added to the transmitted data to ensure errors can be detected and corrected at the receiving end. This means the original message can be read even though it was corrupted during transmission.

Errors can occur not only during the transmission of information via noisy channels but also during the storage of information on a storage medium. In this case, errors are caused by hardware faults, electrical interference, magnetic interference or environmental conditions. As with data transmission, errors are recognised and corrected here by adding redundancy information with the help of error correction codes. [45]

#### 2.3.1. Applications of Error Correction

Among the first users of error correction codes were the then-emerging computer industry and the phone industry. Later, this technology also found increasing use with the advent of space exploration. The payload of early rockets was sometimes limited due to the restricted lifting power. The radius and microwave transmitters, therefore, had comparatively poor performance. Error correction codes were used to solve the problem of the poor quality of the signals received. The National Aeronautics and Space Administration (NASA) used a wide variety of error correction codes for all space missions, including the Reed-Muller code for the Mariner Spacecraft missions between 1969 and 1977, the Golay code for the Voyager 2 flight to Saturn and Jupiter and the Reed-Solomon code for a Voyager mission. Despite efforts to find a universally applicable error correction code, it has been shown that certain correction codes are more suitable for certain applications than others. [46]

Other examples of the use of error correction methods are

- Compact Disks (CDs): Compact discs are used to store data and mainly use the Reed-Solomon code for error correction, although some proprietary methods are also used. [46]

- **Memory modules:** Bits are defined in memory modules by electrical charge stored in "wells". The stored bit becomes faulty if a well unintentionally loses or gains its charge. Such errors occur in memory modules and must be corrected using error correction codes, in this case, often Hamming codes. [45]

- WiFi and Long-Term Evolution (LTE): With both standards, data is transmitted at a high data rate via disturbed channels. Low-Density Parity-Check (LDPC) codes are primarily used for error

correction. [47]

• Hard Drive Disks (HDDs) and Solid State Drives (SSDs): SSD controllers have error detection and correction functions to ensure reliability during data storage. The methods used for NAND flash memory are Hamming Code, Reed-Solomon (RS) Code, Bose-Chaudhuri-Hocquenghem Code (BCH) and Low-Density Parity-Check (LDPC). [48]

#### 2.3.2. Error Correction in Physical Unclonable Functions

With physical unclonable functions, codes are generated from random process variations, which can be used for subsequent authentication processes. However, the values extracted from the PUF are unstable and can vary each time they are used. Due to this variance, the PUF responses cannot be used directly but must first be converted into a usable form. Efficient error correction and key derivation are, therefore, prerequisites for generating secure cryptographic keys using PUFs. Most methods can be divided into linear schemes and pointer-based schemes.

In order to be able to generate reliable keys from the always different PUF responses, helper data must be generated, with the help of which errors can later be detected and corrected using error correction codes. The helper data must be stored permanently on an on-chip NVM or a remote server. In both cases, the helper data's integrity must be ensured to be secure against data manipulation or side-channel attacks. [49]

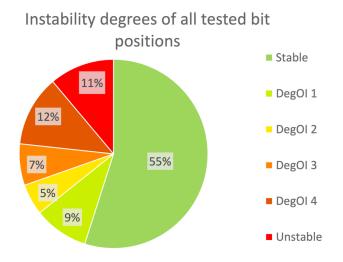

In order to increase the quality of PUFs and simplify error correction, the PUF response actually used can be preselected. When reading out a PUF response, certain sequences may be more stable than others. If the size of the available stable sequences is sufficient, the effectively used PUF value can be reduced to the stable portion, meaning fewer errors must be corrected later, increasing the probability of more reliable data. [49]

## 2.4. Static Random Access Memory (SRAM)

Static Random-Access Memory (SRAM) is a form of computer memory used in microprocessors, general computing applications and electronics. Data is stored statically in SRAM memories and, therefore, does not need to be refreshed, as with Dynamic Random Access Memory (DRAM). Despite this, the data stored in it is volatile, i.e. if the power supply is interrupted, the stored data is lost. Compared to DRAM, SRAM memories are faster but require more space and, therefore, have less usable memory for the same amount of space. [50]

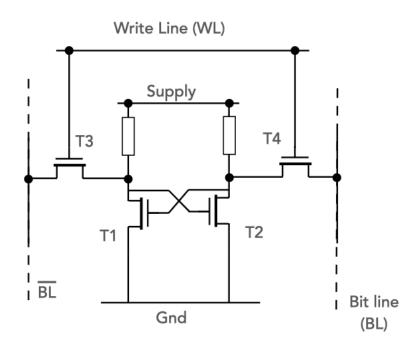

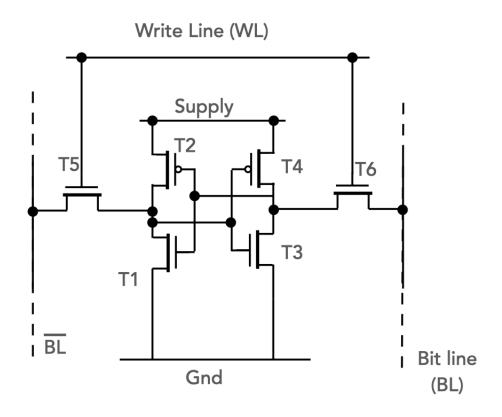

To realise an SRAM cell, transistors in a cross-coupled inverter configuration are generally used. There are different implementation options, which sometimes differ in the number of transistors. One variant of building SRAM cells are so-called four transistor cells (4T) as shown in Figure 2.1. In addition to SRAM cells with four transistors, there are also implementations with six transistors (see Figure 2.2). The two additional transistors are used to control access to the memory cell during read and write operations. This also reduces static power. With only four transistors, a constant current flows through pull-down resistors, increasing the chip's overall power consumption. There are also memory cells with 8 or 10 transistors that utilise additional functions, such as implementing additional ports in a register file, etc., for the SRAM memory. [50]

Figure 2.1.: Four transistor version of an SRAM cell [50]

Several cells are arranged in a matrix, and each cell can be addressed individually. Usually, a series of cells is selected, and their contents are read out in sequence. Cells are often equipped with two-bit lines, one of which returns the bit information and the other the inverse. This serves to guarantee integrity. If the values on both lines are the same, there is an error, and the cell has to be read out again. Access to specific cells is activated by the so-called word line. It controls the access control transistors, controlling the connection between the cell and the bit lines. Both lines are used for read and write access. SRAM and DRAM are among the most commonly used memories. SRAM is often used in microcontrollers and microprocessors as it is faster and requires less power in the idle state. It is also easier to control than DRAM, as there is no

Figure 2.2.: Six transistor version of an SRAM cell [50]

refresh. Although DRAM has a higher storage capacity for the same size, this is not usually required for microcontrollers. Compared to flash memory or Electrically Erasable Programmable Read-Only Memory (EEPROM) technology, SRAM memory also has no limit on the number of read/write cycles, making it perfect for real-time data acquisition applications. [50]

#### 2.4.1. SRAM Based Physical Unclonable Functions

Microscopic variations in the dopant atoms in the channel area of the Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs) cause differences in the threshold voltage of the transistors in an SRAM cell. The transistors that form the cross-coupled inverters are designed to be exceptionally weak, allowing them to switch from 0 to 1 easily during a write operation. For this reason, these transistors are highly susceptible to intrinsic fluctuations at an atomic level, which are not under the control of the manufacturing process and are independent of the position of the transistor on the chip. The read and write process is not affected in regular operation as the SRAM cells are designed with appropriate width/length ratios between the individual transistors. During the power-on process, the cross-coupled inverters in an SRAM cell are not exposed

to any external signal influence. Therefore, due to intrinsic parameter deviations of the transistors, even the slightest voltage differences tend to become either a 0 or a 1. This is due to the amplification effect of the inverters acting on the output of the other inverter. For this reason, the probability is relatively high that the same SRAM cell will start in the same state after being switched off and on again. However, the individual SRAM cells behave independently of each other. [30] A binary string is obtained if the random states of a large number of SRAM cells are read out directly after switching on. This binary character string is unique for each SRAM memory due to production variations at the atomic level and can, therefore, be seen as a kind of digital fingerprint. In contrast to other PUF implementations described in the literature, the binary string can be used directly without going through a quantisation process. This reduces the complexity of the measurement circuit and makes SRAM memory an ideal candidate for PUFs. [30]

The binary strings read from the uninitialised SRAM memory are random and can be used as cryptographic keys after processing (including error correction). As an alternative to storing cryptographic keys in non-volatile memory, PUFs are more resistant to physical attacks because the information disappears whenever the device is powered off. It is also impossible to produce an exact physical copy of the memory due to its atomically unique characteristics (hence physical unclonable function - PUF). [51]

## 3. Related Work

SRAM PUFs are receiving considerable attention from the research community due to their promising application in embedded systems security and the Internet of Things. They have been researched for over a decade and are already in use in a wide variety of areas such as Aerospace & Defense [1], Automotive Security [52], Medical Equipment [53], Industrial IoT [54], Health, Wearables, Smart grid, Home [55] and more.

SRAM PUFs use atomic level production differences to create a kind of digital fingerprint that cannot be physically copied due to its properties. They offer a unique, secure alternative to traditional cryptographic keys stored on non-volatile memory and could be read by potential attackers with appropriate effort. However, there are some challenges to overcome, such as the instability of individual cells, finding suitable error correction methods, problems due to silicon ageing effects, and secure derivation of cryptographic keys, which are the subject of past and current research.

This chapter presents some of the most relevant papers for this master thesis, including their results. It discusses the general security of SRAM PUFs, reviews the stability of the individual cells under different circumstances, explains selection methods for stable bits in the PUF response and examines how other researchers have proposed a secure authentication method based on the SRAM PUF.

At the beginning of the work for this master thesis, there was primarily research on SRAM PUF measurements and implementations for complex Field Programmable Gate Arrays or external SRAM memories, but little research on the use of SRAM PUF on commodity hardware like the ESP32. However, while writing this thesis, several papers and software were published in this regard. However, most are focused on measuring and analyzing the PUF responses and not on developing an authentication method. One paper [56] deals with both SRAM PUF measurements and analysis and an authentication method for the ESP32; this is discussed in more detail in a subchapter.

#### 3.1. Intrinsic ID

Intrinsic ID is a company that specializes in security Intellectual Property (IP) for embedded systems based on PUF technologies. Their IP can be delivered in software or hardware and applies to virtually any chip. It is used as a hardware root of trust to validate payment systems, ensure secure connectivity, authenticate sensors, and protect sensitive government and military data and systems. Their solutions are used and certified on millions of devices, including EMVco, Visa, CC EAL6+, PSA, IoXT and governments worldwide. [57]

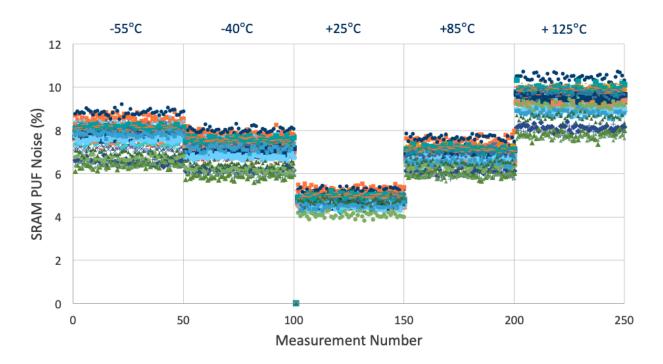

#### 3.1.1. Silicon Ageing

Over time, an Integrated Circuit (IC) changes due to ageing processes. These physical changes usually alter the circuit's functionality, resulting in degradation that can ultimately lead to the failure of the entire IC. The most important degradation effects include Negative Bias Temperature Instability (NBTI), Hot Carrier Injection (HCI), Electromigration and Time-Dependent Dielectric Breakdown (TDDB). Ageing effects like these reduce the reliability of a PUF over time and lead to multiple failures. Intrinsic-ID tested the ageing effects by exposing ICs to high temperatures (80°C) and high voltage for 130 days and checking SRAM PUF values against reference values at room temperature. The noise in the SRAM PUF increased from 5% to almost 15% in this test. [58]

#### 3.1.2. SRAM Aging Mitigation (Anti-Ageing)

Anti-ageing strategies have been developed to counteract the effects of ageing and ensure the reliability of SRAM PUFs without affecting PUF quality, safety, or efficiency. One possible solution for anti-ageing is to write the opposite value of an SRAM cell after power-up. If an SRAM cell adopts the value 0 after power-up, 1 is written to this address and vice versa. Intrinsic-ID experiments showed that the noise in the PUF drops to below 10% almost immediately after applying these anti-ageing procedures and follows a further downward trend over the next 100 days. If such anti-ageing procedures are applied from the start, they can also reduce the natural PUF noise. [58]

#### 3.1.3. Influence of Temperature Variation

Since 2003, Intrinsic-ID has conducted billions of SRAM PUF measurements from manufacturers and production facilities worldwide to measure noise behaviour. These tests were carried out at temperatures between -55°C and +125°C. The results show that at a room temperature of around 25°C, the PUFs exhibited

the lowest noise behaviour, and at a temperature of +125°C, the highest. The diagram in Figure 3.1 shows the sensitivity of the SRAM PUF noise at changing temperatures as part of a typical temperature fluctuation measurement for military applications. [58]

Figure 3.1.: Influence of temperature variation on SRAM PUF noise [58]

The research results of Intrinsic-ID provide a profound insight into the behaviour of SRAM memories. Compared to this work, their long-term measurements were conducted over a significantly longer period and in considerably higher numbers. Due to their vast data set, they can draw more meaningful conclusions and provide more accurate information. However, their research mainly tested commercially available memory modules. In contrast, the integrated Real Time Clock (RTC) slow memory SRAM of the ESP32 was tested as part of this master's thesis, which means that more precise information can be provided for this specific microcontroller.

# 3.2. Systematic Bit Selection

The authors of "A Systematic Bit Selection Method for Robust SRAM PUFs" [51] proposed a method for selecting reliable SRAM cells for PUF applications. In addition, they investigated the impact of ageing effects, temperature and voltage variations on the stability of SRAM cells.

# 3.2.1. Ramp Rate Impact on Reliability of SRAM PUF

The ramp rate is the rate at which the SRAM memory is supplied with the supply voltage. Theoretically, the power supply from the Virtual Switching System (ground) (VSS) to the Drain to Drain Voltage (VDD) can be established very quickly, in nanoseconds or less, or very slowly, over several seconds. With a fast ramp rate, particular MOSFETs in the SRAM are neglected; with a fast ramp rate, all MOSFETs are taken into account, resulting in different power-up values in the various cells. The values that an SRAM cell assumes after a power-up can, therefore, sometimes depend on the respective ramp rate. Cells that display inconsistent values at different ramp rates are potentially unstable.

# 3.2.2. Data Retention Voltage for Strong Cell Selection

In the classic data retention test, the most unstable SRAM cells are identified by writing a 1 to all cells and then reducing the power supply to a critical level. The low current supply is maintained for a while and then increased to the initial value. All cells are then read out. Some unstable cells cannot retain the stored values and change their values to 0. Cells that return a 0 after this test have a very strong tendency towards this value and will most likely also adopt this value during a power-up. The same experiment can be carried out for cells with a strong tendency towards 1 by writing all 0 in the cells and repeating the experiment.

The cells that change their value from 1 to 0 or vice versa at a critically low power supply tend to be strong candidates for PUF, as they are strongly biased and are very likely to take their values at a power-up.

### 3.2.3. Their Results

The authors of [51] performed some tests to evaluate the power-up stability and reliability. For this purpose, commercially available 64 KBit chips were used, and the power-up time of the SRAMs was controlled using a function generator that allowed the power-up time to vary from 7ns to 100s. However, a consistent power-up time of 7ns was used for the tests. The data retention test described above was carried out in the first test, and the stable bits (which change their value when the power supply is critical) were identified. The state of these cells was then tested after a power-up at different temperatures (25°C, 50°C and 85°C). A ThermoSpot direct contact probe system was used for this purpose. The chips were activated 1000 times at all temperatures, and the states of the cells were measured. It was found that the number of unstable cells increased at high temperatures. The same experiment was then carried out with different supply voltages. Here, it was found that the number of unstable cells decreases when the supply voltage is increased. Finally, the authors tested the ageing effect of the cells. Here, 40% of the SRAMS was initialized with the value 1

and 60% of the SRAM with the value 0. They then read out the start-up values of all SRAM chips 1000 times to check the reliability of the selected cells. It was found that with sufficient supply voltage (0.58V), all previously selected stable cells were still stable. Controlled ageing, therefore, did not cause any deterioration in the stability of cells that were already stable beforehand.

As part of their research, a bit selection procedure was presented that can be used to find the stable bits in an SRAM that remain stable even with a change in circuit noise, voltage, temperature changes and ageing. The proposed bit selection procedure offers a promising solution for identifying stable bits. Unfortunately, these results could not be verified within the scope of this master's thesis. The RTC SLOW memory SRAM is embedded, so the direct current supply and the ramp rate cannot be controlled. Nevertheless, the results provide indirect help in finding stable bits. Essentially, external interference factors are deliberately used, and the SRAM values are regularly compared with each other to find stable bits. In this master's thesis, stable cells were extracted based on the long-term measurements, the measurements at different temperatures and the measurements at different voltage supplies.

# 3.3. Vulnerabilities of Memory-Based PUFs

The security of PUF keys is based on two features: uniqueness and uniformity. Uniqueness states that if at least two devices generate a PUF response, these must be random, and the difference between these two responses should have a Hamming distance of around 50%. Uniformity means that the distribution of 0 and 1 in a PUF response should be uniform. To achieve this, the Hamming weight of the PUF responses should be close to 50%. However, [59] showed that this uniform distribution is not sufficient and opens attack vectors.

[59] addresses several aspects of memory-based PUFs that they claim have been overlooked by research.

They identify that the PUF responses of architectural and layout similarities of SRAM chips from the same manufacturer with the same model number have correlations. To save costs, many manufacturers also reduce the size of SRAM memories, making them more susceptible to failure and less robust. Some of the different SRAM cell structures (e.g. 4T, 5T, 6T, 7T, 8T and 9T) sometimes lead to biased results. Although symmetric SRAM architectures are the preferred choice of SRAM PUFs, they can produce deterministic, biased outputs due to asymmetric manufacturing technologies.

Process variations are intrinsic phenomena in the manufacturing process that introduce variability (for example, through transistor attributes, interconnect lines, and dielectric layers). The systematic variations cor-

relate with the chip's layout, the silicon wafer's characteristics, the manufacturing site and the technology. However, the random process variation is entirely indeterministic. Patterns can be learned from systematic process variations through statistical analysis. These patterns significantly influence the start data in the SRAM, which can lead to a bias.

To summarize, architectural similarities in SRAM memory and process variations can compromise the security and uniqueness of memory-based PUFs. These circumstances create deterministic and correlating properties, increasing vulnerability to non-invasive attacks by allowing the deterministic properties to be used as side-channel information.

The authors of [59] also found that the use of error correction techniques commonly used in PUF applications can contribute to lower PUF security. Since SRAM PUFs primarily use noisy data and a certain percentage of SRAM cells are unstable, the unstable values are, in many cases, corrected using error correction techniques. As fewer bits are now relevant for generating a PUF response, attacks are more accessible as they result in a much smaller number of patterns to be tested. This reduces the time and resources required by an attacker.

To ensure the security of a PUF, these should ideally have an even distribution of 0 and 1 across all bit positions. This results in a binomial distribution of responses, which, if implemented correctly, resembles a Gaussian distribution. In practice, however, this is not checked sufficiently, which can lead to distortions. If the standard deviation is not adjusted precisely, this can impair the reliability of the PUF. The authors recommend carefully checking the response distribution's uniformity to ensure that the PUF responses are genuinely random and uniformly distributed.

# 3.3.1. Mitigations

To ensure the security of PUFs, the authors of [59] recommend the following four measures:

- Avoiding Error Correction Schemes: Error correction schemes reduce entropy and increase attack risk. If error correction schemes are omitted, attackers have to guess exact answers and cannot quickly reduce the number of possible patterns. There are ways to make error correction unnecessary through specific SRAM designs and selection methods, increasing security, but these approaches are technically more demanding and only sometimes applicable.

- Using Properly Designed Fuzzy Extractor: Fuzzy extractors are often used to correct errors and improve security. The authors recommend using fuzzy extractors that strictly follow the fuzzy min-

entropy boundary condition. Some simple fuzzy extractors convert a fixed-length input into a fixed-length output but do not consider the min-entropy, thus jeopardizing security.

- Pattern Distribution-Aware Challenge Response Pairs (CRPs): As mentioned before, the bit patterns should have an even distribution of 0 and 1. The authors recommend selecting SRAM addresses during the login and registration phases to ensure an even distribution of all possible responses.

- Locality-Aware Challenge Response Pairs (CRPs): PUF responses generated from specific logical address segments may be more vulnerable than those from other segments. A heuristic attack can be prevented by selecting less vulnerable logical address segments for the generation of CRPs. If an attacker knows the exact layout of an SRAM, this could also pose a risk. It is, therefore, the responsibility of SRAM manufacturers to provide concrete guidelines for the use of PUFs, as only they have precise knowledge of the physical layout of the SRAM.

The results and in particular the mitigations from this paper are essential for this master's thesis. Based on the results, error correction schemes and fuzzy extractors were dispensed with in the authentication system and a bit selection scheme was used instead. Furthermore, the distribution of 0s and 1s in the SRAM was verified, the Hamming weight was selected as the central factor for the security of the SRAM PUF, and the uniqueness between the SRAMs was meticulously inspected by all the microcontrollers tested.

# 3.4. SRAM PUF on the ESP32 Microcontroller

The paper "ESPuF - Enabling SRAM PUFs on Commodity Hardware" [56] was published in September 2023, during the writing of this thesis. The research topic of the paper shows strong similarities to this master thesis. It addresses the implementation of Static Random-Access Memory Physical Unclonable Function (SRAM PUF) based authentication for ESP32 microcontrollers, the same topic as in this thesis. The researchers conducted a comprehensive literature review, performed measurements on several different microcontrollers of the same type and both confirmed and disconfirmed some assumptions from the literature, developed a proof-of-concept for SRAM PUF-based authentication, and then wrote some security concerns and recommendations for future changes to the microcontrollers used.

The authors particularly opted for the ESP32 microcontroller, as many other researchers primarily use expensive Field Programmable Gate Array (FPGA) boards or similar complex hardware. However, such complex hardware is unsuitable for low-cost deployments and is barely used in real-world applications. ESP32

microcontrollers are inexpensive, have built-in SRAM and are already built into a variety of devices, making them the ideal microcontroller for SRAM PUF authentication use cases.

The authors refer to a statement in [60], in which it is mentioned that after 16 successful startup iterations, individual SRAM cells can already be classified as stable or unstable. However, this statement is not substantiated in the reference paper [60], and the measurement results also refute this statement.

# 3.4.1. Authentication System

The main goal of their concept is to authenticate an ESP32 microcontroller based on the internal SRAM PUF. Due to a single challenge-response pair (CRP), the SRAM PUF is classified as a *weak PUF* and is directly used to derive a secret key. However, due to the use of Elliptic Curve Cryptography, the *weak* characteristic is removed.

The concept of the paper presumes that the manufacturer already performs PUF measurements on the microcontrollers and creates a PUF challenge. Alternatively, the authors mention that a motivated developer can carry out the measurements, but this process is extensive. The manufacturer or a developer must first create a PUF challenge. The PUF challenge is a bit mask that specifies which specific bits in the SRAM are stable (do not change) and unstable (can change during several power-on processes). An authentication server must also be provided, which derives and stores a shared secret when the PUF challenge is created using the discrete logarithm problem. This shared secret does not need to be stored on the microcontrollers, as it can be generated automatically using the PUF when the microcontroller is powered on without being stored on the device.

They tested a total of seven ESP32s in three different variants:

- AZ-Delivery ESP32 DevKit C V4

- Heltec Wi-Fi LoRa 32 (V1 and V2)

- WT32-eth01

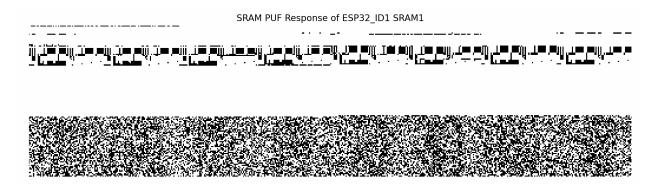

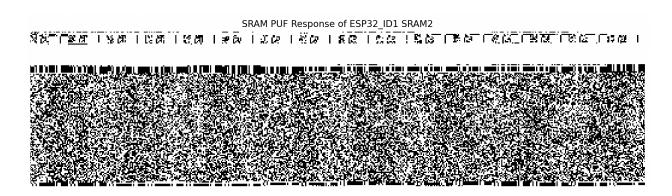

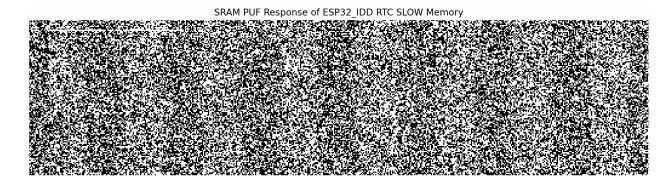

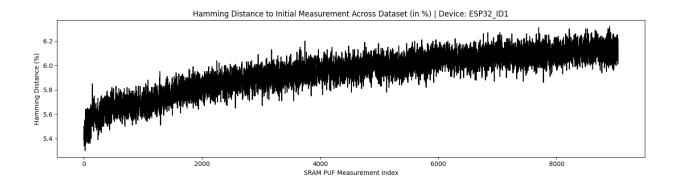

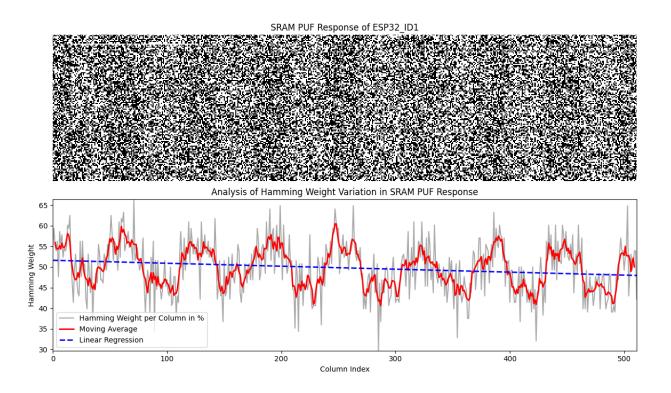

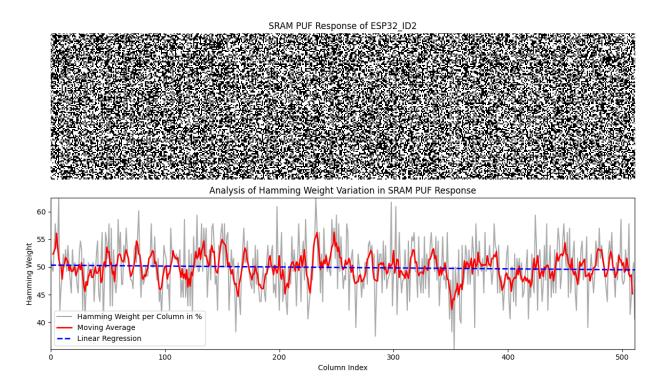

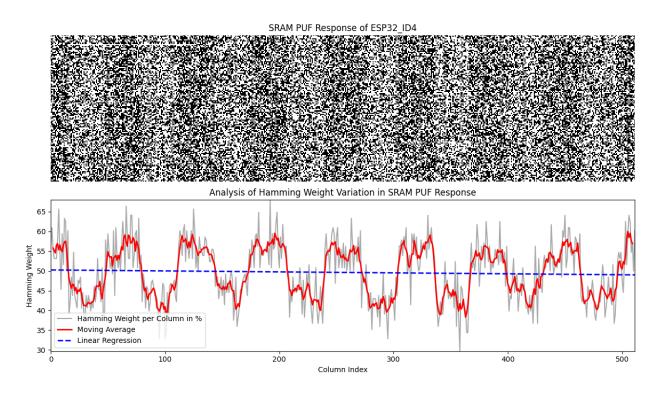

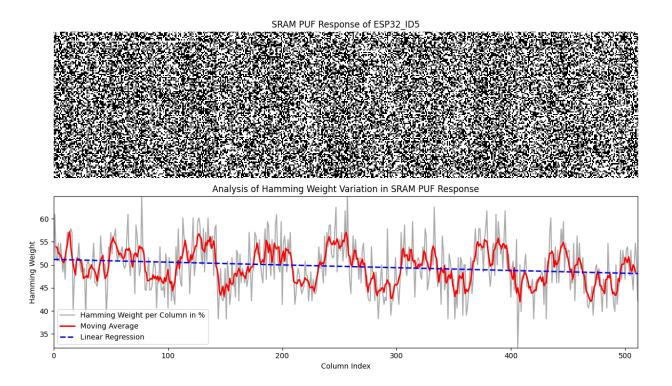

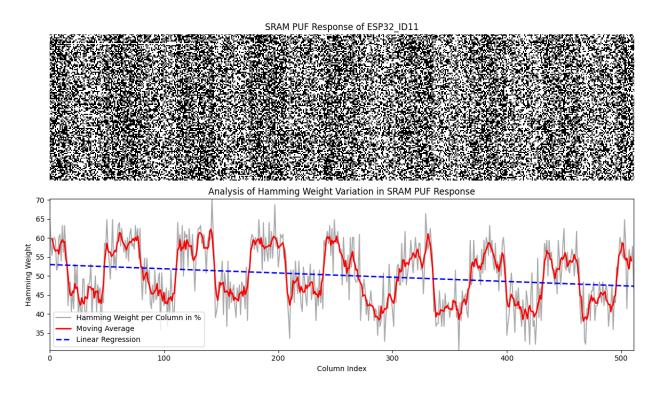

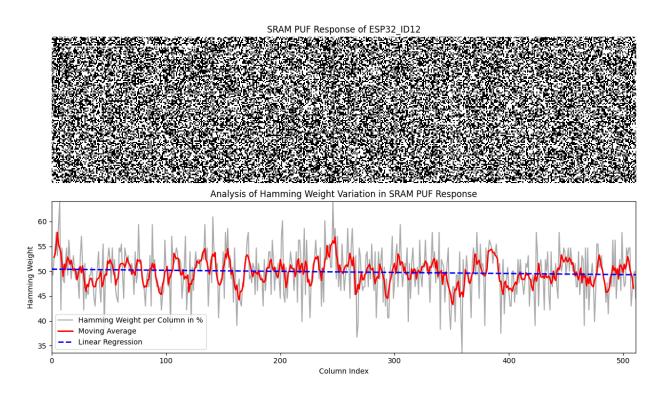

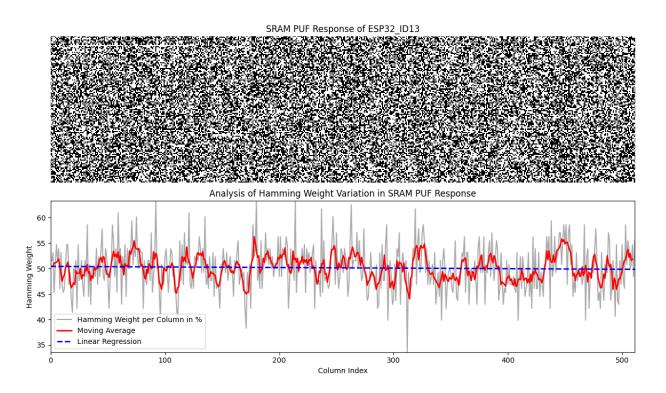

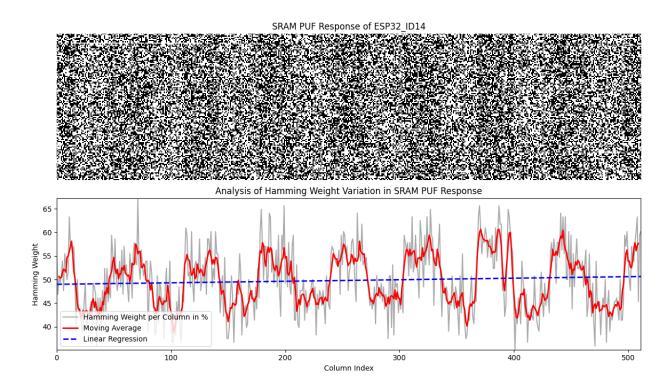

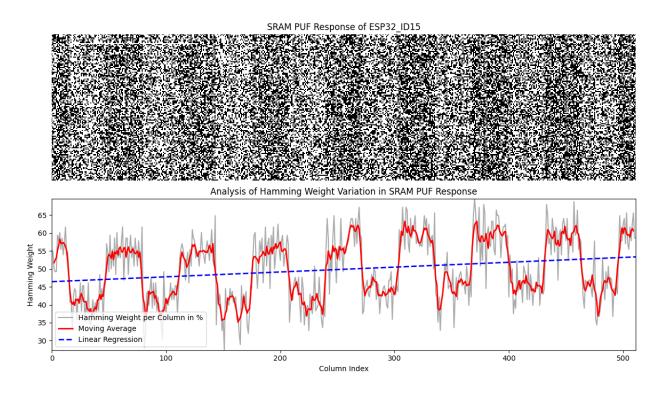

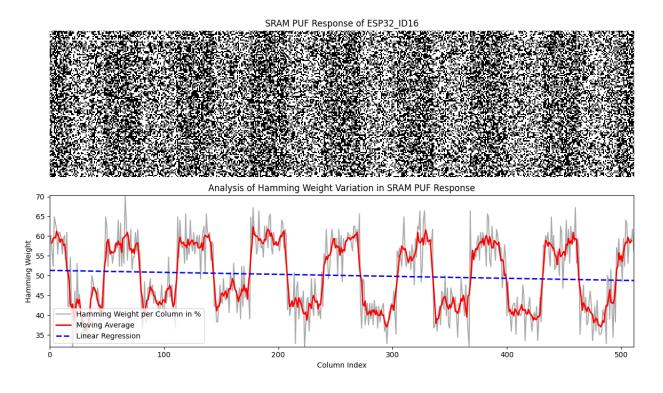

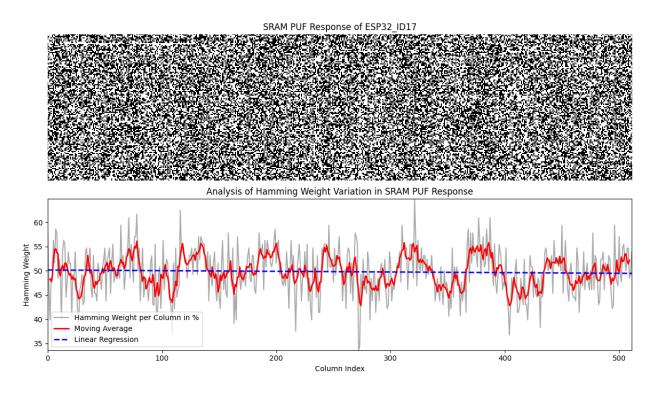

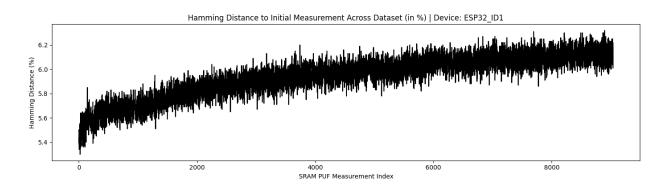

The ESP32 has two integrated SRAM sections, with the first (SRAM1) having a memory of 128KB and the second (SRAM2) having a memory of 200 KB. Only SRAM 1 was used for their tests, and only the first 128 bits were read. They justify this by pointing out that 64-bit SRAM PUF security is sufficient for most applications and that, according to studies, the first 128 bits already have sufficient entropy. The same firmware was flashed onto all test devices for the tests, which underwent 1000 PUF iterations. When analysing the results, the researchers found that across all of the tested microcontrollers, the number of stable bits at 1000